## Description

CambridgeIC's CAM502 Central Tracking Unit (CTU) IC is a single-chip processor for precise position measurement. It implements the electronic processing for resonant inductive position sensing technology. The CAM502 is optimised for high-speed applications.

The CTU measures the position of a contactless, inductively coupled target relative to a sensor that is built from a printed circuit board to CambridgeIC's design.

## Features

- Resonant inductive position sensing engine

- Fully ratiometric measurements

- Automatic tuning to target frequency

- SPI communications (slave device)

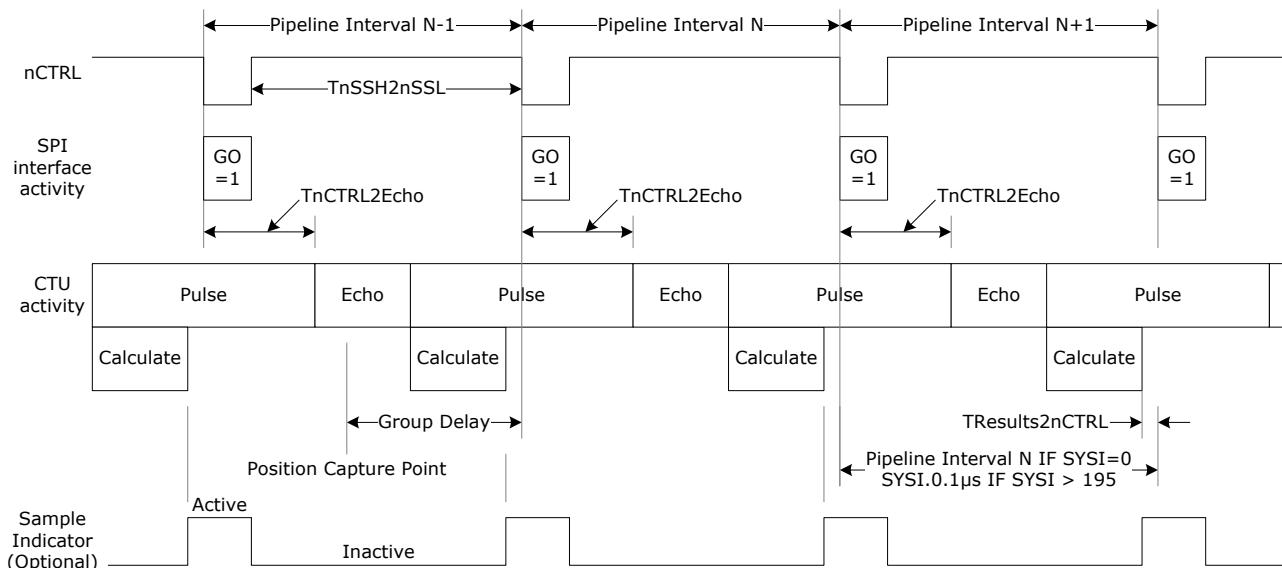

- Pipeline measurement for high-speed operation

- Control input for synchronising measurements

- User IOs for position triggers and sample indicators

- Internal software upgradable over SPI

- Works with Type 2 and 6 sensors

- External crystal controlled timing

## Performance

- Group Delay physical position to SPI ready  $\leq 140\mu\text{s}$

- Up to 5100 independent samples per second

- SPI interface bit rate up to 10Mbit/s

- Up to 15 bits noise free resolution without filtering

- Up to 18 bits noise free resolution with filtering

## Applications

- Position feedback for high-speed motion control

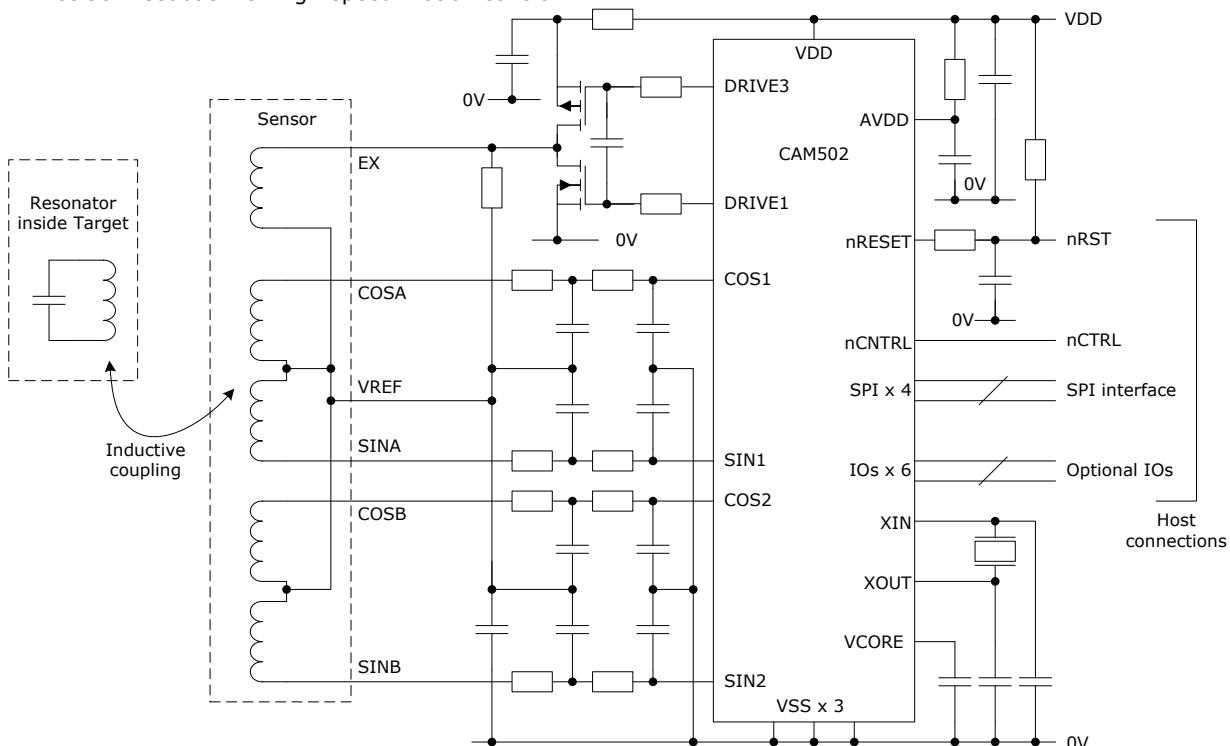

Figure 2 Circuit for reading a Type 6 sensor

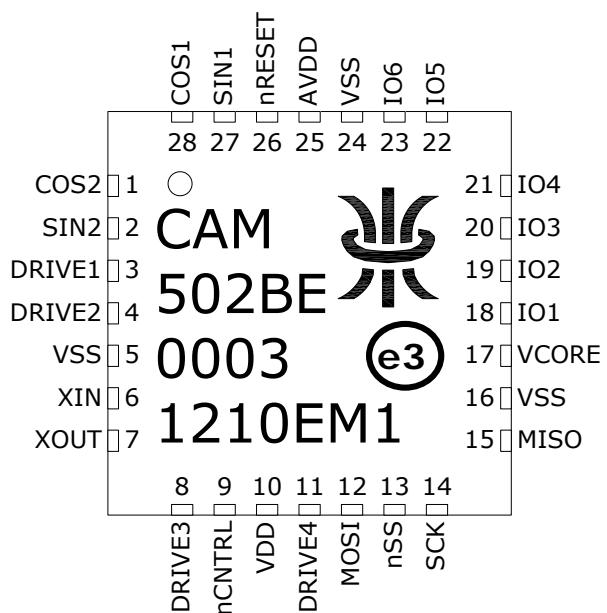

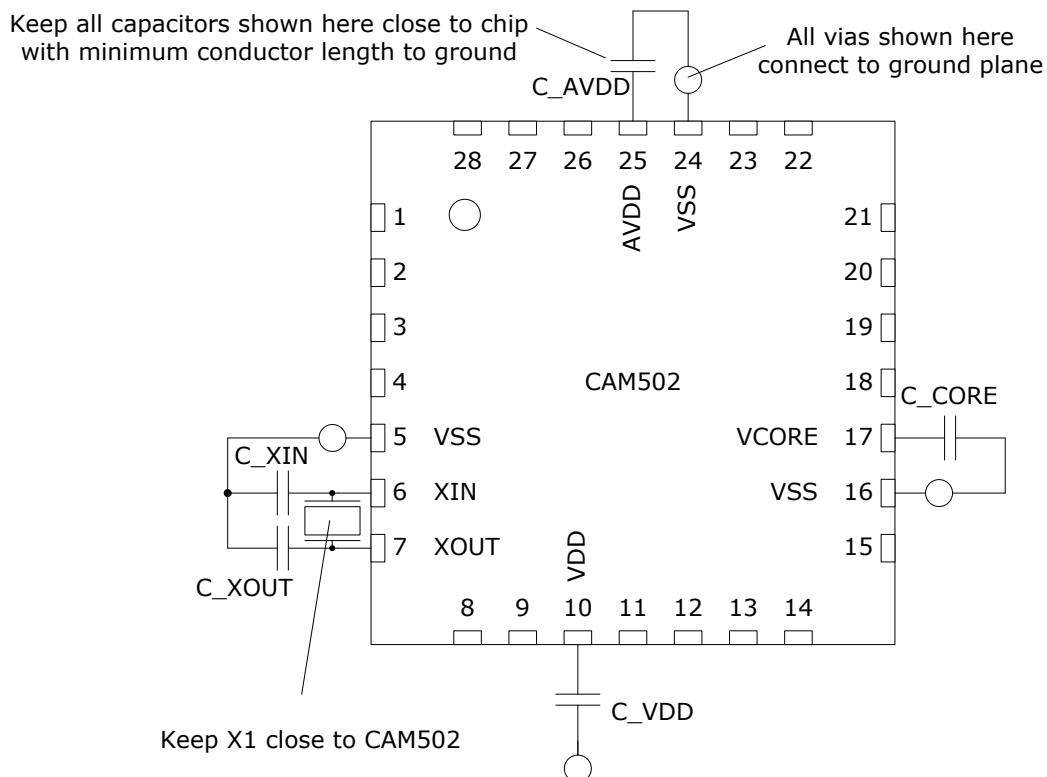

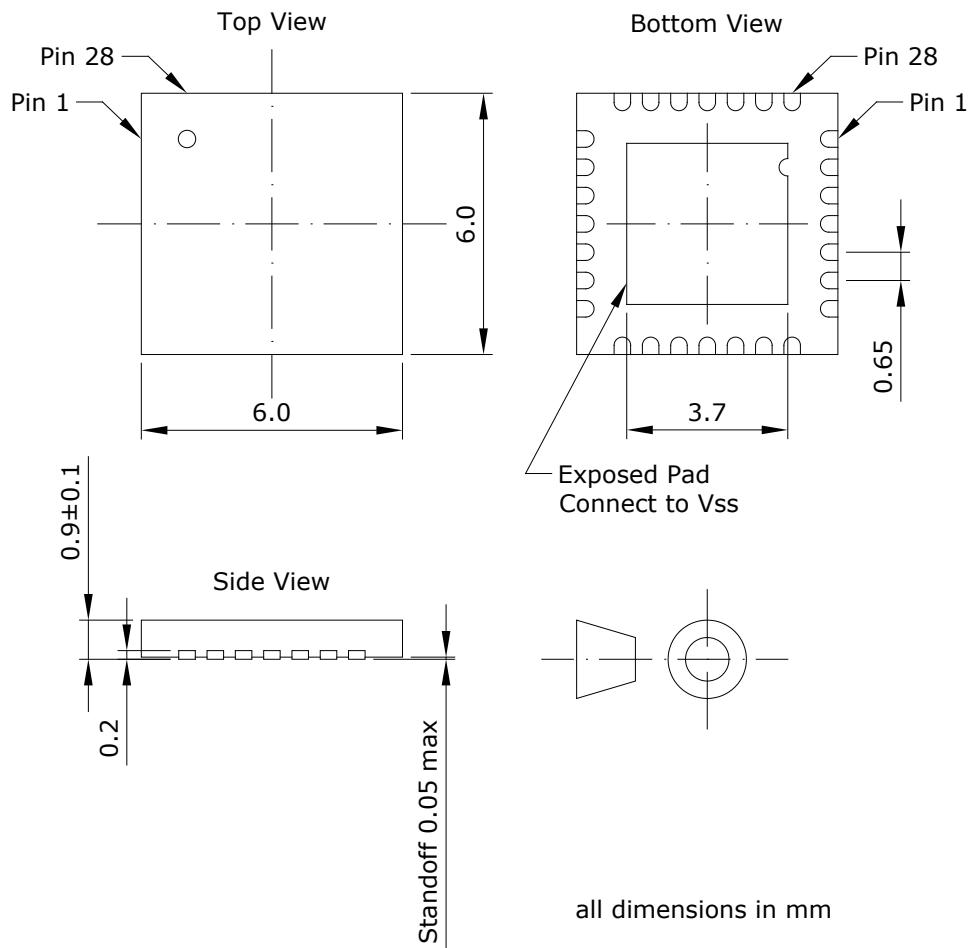

Figure 1 CAM502 28-pin QFN pinout

| Product identification |                                           |

|------------------------|-------------------------------------------|

| Part no.               | Description                               |

| CAM502BE-0003          | CAM502BE in 28-pin QFN<br>-40°C to +125°C |

## 1 CAM502 Functional Description

### 1.1 Overview

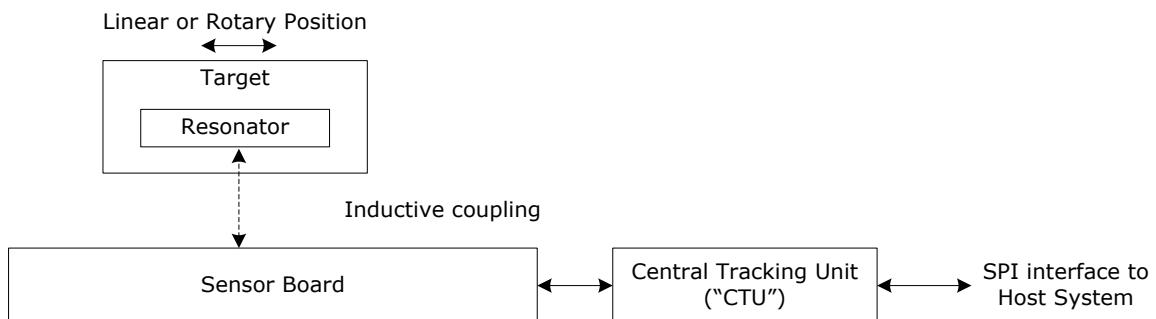

The CAM502 Central Tracking Unit (CTU) works with a sensor built from a PCB to measure the position of a contactless target. Targets comprise an inductively coupled resonant circuit. Sensors are available for linear and rotary measurement and in a range of different sizes.

**Figure 3 resonant inductive position sensing system**

Sensor Types differ in their details, but the same basic measuring principle applies to them all. The CTU generates signals that drive external miniature MOSFETs. These, in turn, drive AC current into the sensor's excitation coil. The excitation coil current generates an AC field which powers the resonator at its resonant frequency. The energy in the resonator is built up during this pulse.

Then the current is removed, and the resonator induces decaying EMFs in the sensor coils. The CTU detects the amplitude of this echo in each sensor coil. It then uses the amplitude values to calculate position.

The details of the measuring process and calculation depend on sensor Type. In all cases, sensing and calculation are fully ratiometric for immunity to changes in amplitude due to gap, misalignment, temperature, target frequency and supply voltage.

The pulse echo interrogation method separates the excitation and detection processes in time. This yields immunity from stray coupling between excitation and sensor coils, and superior sensing performance.

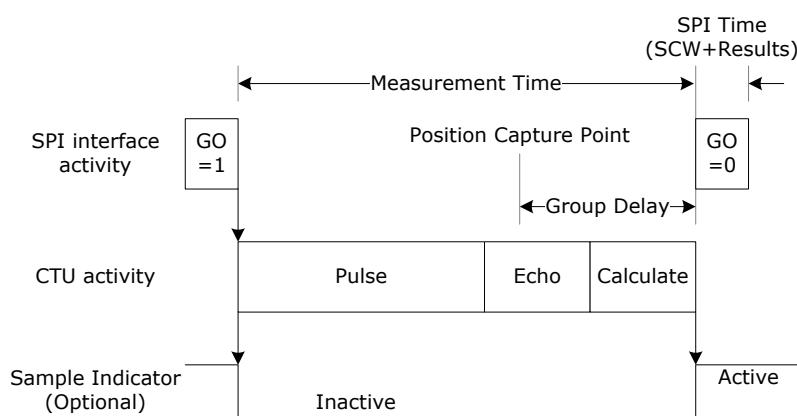

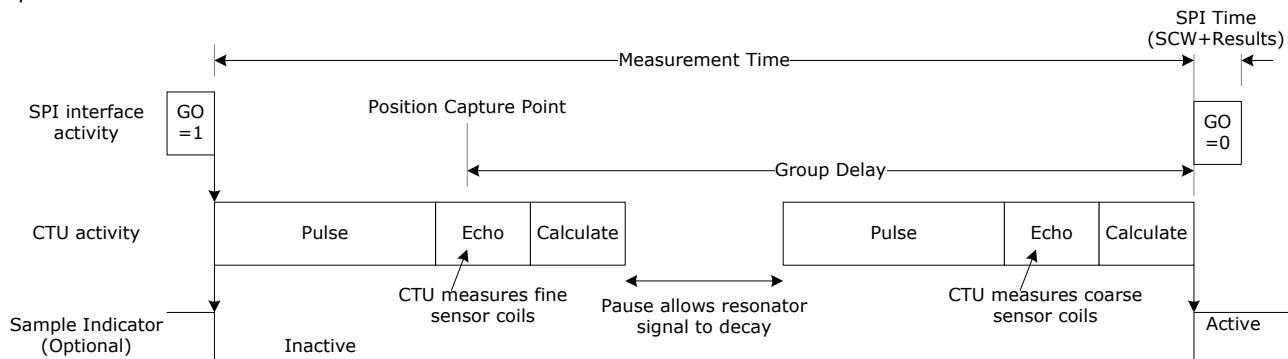

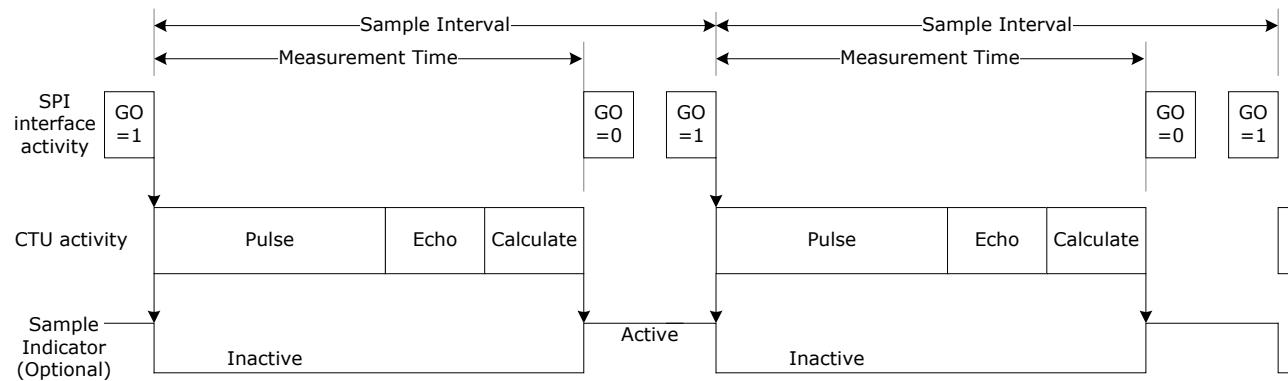

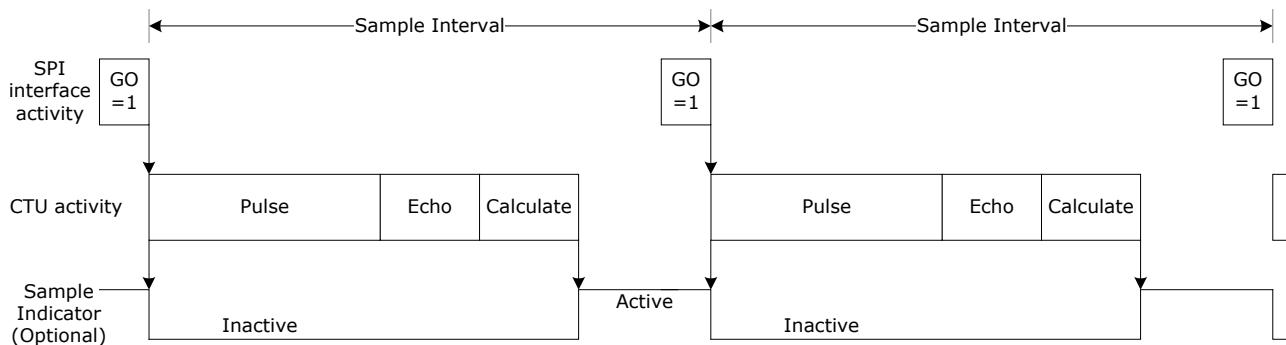

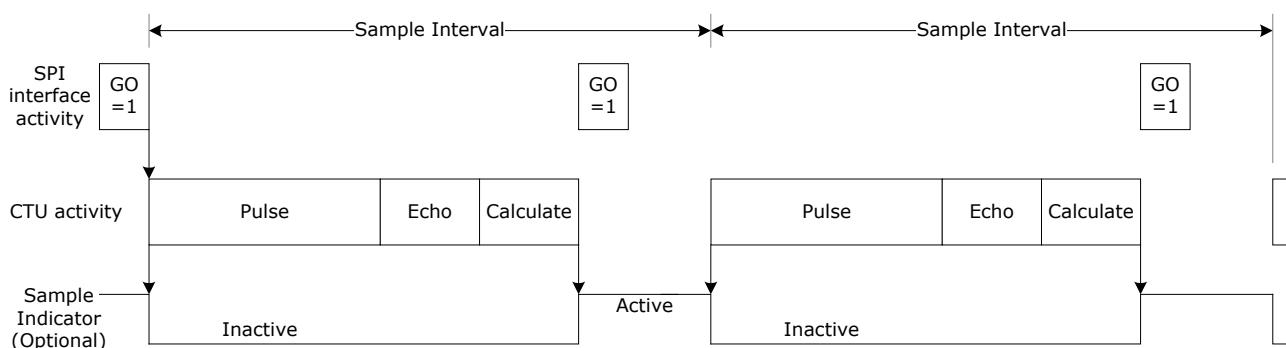

**Figure 4 Electronic measuring process**

## 1.2 Sensor Types

Table 1 lists the sensor types currently supported by the CAM502, and includes section references for more details on each Type.

Table 1 Comparison of sensor types

| Type | Number of coils in each sensor |         | Application              | Max number of sensors (CAM502) | Has Subtypes? | Section number for details |

|------|--------------------------------|---------|--------------------------|--------------------------------|---------------|----------------------------|

|      | Excitation                     | Sensing |                          |                                |               |                            |

| 2    | 1                              | 4       | Long linear sensors      | 1                              | No            | 3                          |

| 6    | 1                              | 4       | Precision rotary sensors | 1                              | Yes           | 4                          |

## 1.3 Pin Names and Functions

Table 2 summarises CAM502 pin functions and type. Please refer to section 2 for electrical characteristics for each type.

Table 2

| Signal Name              | Type                                      | Function                                                                                                  |

|--------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| VDD                      | Power                                     | Positive supply voltage.                                                                                  |

| AVDD                     | Analog Input                              | Analog supply voltage, decoupled from VDD.                                                                |

| VSS (x3)                 | Power                                     | 0V connection and common return for sensor inputs.                                                        |

| VCORE                    | Power                                     | Output of on-chip 2.5V regulator, requires external decoupling capacitor to VSS.                          |

| nRESET                   | Digital Input, 5V Tolerant                | Hardware reset, active low                                                                                |

| nSS                      | Digital Input, 5V Tolerant                | SPI Interface line: Slave Select, active low.                                                             |

| SCLK                     | Digital Input, 5V Tolerant                | SPI Interface line: Serial Clock.                                                                         |

| MOSI                     | Digital Input, 5V Tolerant                | SPI Interface line: Master Out, Slave In.                                                                 |

| MISO                     | Digital Output, 5 V Tolerant (1)          | SPI Interface line: Master In, Slave Out.                                                                 |

| IO1 and IO2              | Digital or Open Drain Output, 5V Tolerant | User configurable IO.                                                                                     |

| IO3, IO4, IO5 and IO6    | Digital or Open Drain Output              |                                                                                                           |

| nCNTRL                   | Digital Input                             | Control pin, optionally used to synchronise measurements                                                  |

| DRIVE1 – DRIVE4          | Digital Output                            | Used to drive external MOSFETs for powering the excitation coil of the resonant inductive position sensor |

| COS1, COS2<br>SIN1, SIN2 | Analog Inputs                             | Used to sense the sensor coil outputs of resonant inductive sensors.                                      |

| XIN, XOUT                | Analog                                    | Connections to external crystal                                                                           |

| Exposed Pad              | Shield                                    | Large pad under package (Figure 45). Connect to Vss.                                                      |

Note (1): MISO is driven as a digital output by the CAM502 during SPI transactions (nSS low), and is Open Drain at other times to allow other slave devices to share the SPI bus.

## 2 Electrical Characteristics

### 2.1 Operating Characteristics

Table 3 operating characteristics

| Item                               | Min     | Max   | Comments                      |

|------------------------------------|---------|-------|-------------------------------|

| Operating Supply Voltage VDD, AVDD | 3.0V    | 3.60V |                               |

| Operating Temperature              | -40°C   | 125°C | Ambient temperature, CAM502BE |

| VDD start voltage relative to VSS  |         | 0V    | For reliable power on reset   |

| VDD rise rate relative to VSS      | 0.1V/ms |       |                               |

### 2.2 Absolute Maximum Ratings

Table 4 absolute maximum ratings

| Item                                        | Max                 |

|---------------------------------------------|---------------------|

| Voltage between VDD or AVDD and VSS         | -0.3V to +4.0V      |

| Voltage on 5V Tolerant pins relative to VSS | -0.3V to +5.6V      |

| Voltage on any other pin relative to VSS    | -0.3V to (VDD+0.3V) |

| Current into or out of Digital Output       | 4mA                 |

### 2.3 Digital Input Specifications

Table 5 digital input specifications

| Item                        | Min       | Max       |

|-----------------------------|-----------|-----------|

| Input Low                   | VSS       | 0.2 x VDD |

| Input High, 5V Tolerant     | 0.7 x VDD | 5.5V      |

| Input High, NOT 5V Tolerant | 0.7 x VDD | VDD       |

| Input leakage current       |           | ±4µA      |

### 2.4 Digital Output Specifications

Table 6 digital output specifications

| Item                                         | Min  | Max  | Comments            |

|----------------------------------------------|------|------|---------------------|

| Output Low Voltage                           |      | 0.4V | IOL = 2mA           |

| Output High Voltage (Digital setting)        | 2.4V |      | VDD=3.3V IOH = -2mA |

| Output High Current (Open Drain setting)     |      | ±4µA |                     |

| Output High Voltage, Open Drain, 5V Tolerant |      | 5.5V |                     |

| Output High Voltage, Open Drain              |      | VDD  |                     |

### 2.5 Application Memory Characteristics

The CAM502 includes a processor with FLASH memory. This can be updated with new Application Code over its SPI interface, see section 10. It can also be updated with new Configurable Defaults, see section 9.13. FLASH memory related specifications are in Table 7 below.

Table 7 application memory characteristics

| Item                    | Min      | Max  | Comments                                                  |

|-------------------------|----------|------|-----------------------------------------------------------|

| Number of FLASH updates |          | 2000 | Across Operating Supply Voltage and Operating Temperature |

| Retention time          | 20 years |      |                                                           |

### 3 Type 2 Sensor Application

Type 2 sensors are for the precise measurement of linear position. Please refer to sensor datasheets for more information.

#### 3.1 Circuit Schematics, Type 2

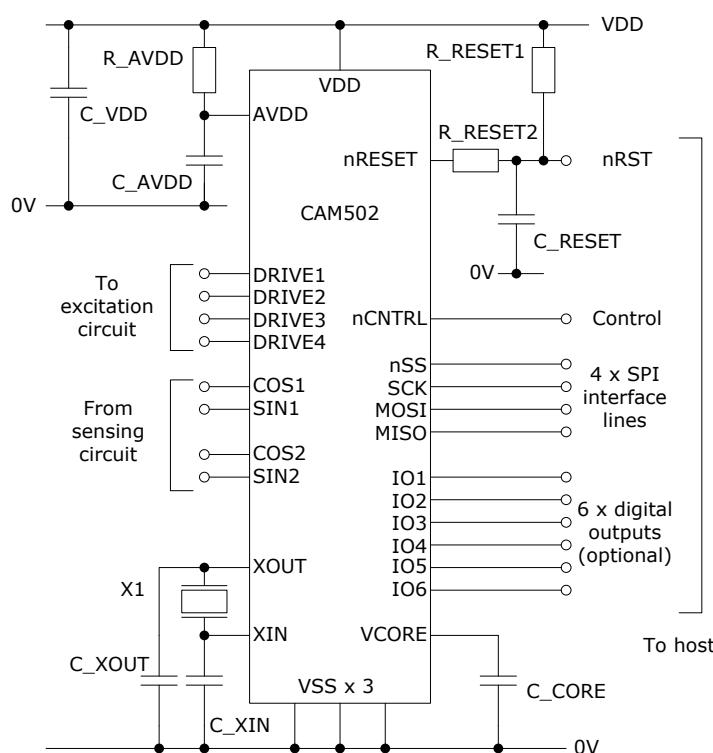

Figure 5 shows how the CAM502's supplies should be connected, the chip's connections to the host and to the excitation and sensing circuits. Component values are listed in Table 8.

VCORE is an external connection to an on-chip 2.5V regulator. This pin requires an external decoupling capacitor. It must not be connected to other circuitry.

AVDD is the analog supply input to the CAM502, and is used as a reference voltage. The values of R\_AVDD and C\_AVDD are important for the CAM502 to operate to full specification.

nRESET requires a series resistor R\_RESET2 for current limiting in the event of ESD, a pull-up resistor R\_RESET1 and a reset timing capacitor C\_RESET. The host may also perform a reset, by pulling the signal nRST low with an open drain output. Connecting the reset line in this way simplifies bootloader operation (section 10).

MISO requires a pull-up resistor of  $4.7\text{k}\Omega$  if this is not provided by the host.

The CAM502 uses an external crystal, X1, to derive precise timing.

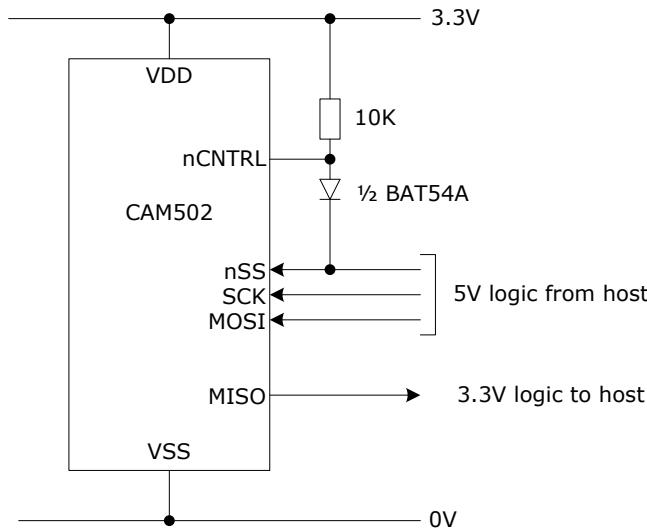

The nCNTRL pin is for measurement control. It must be connected to nSS in pipeline mode with CONT=0 (section 9.7) so that measurements are synchronised to the host's acquisition of position data over the SPI interface. nCNTRL is not 5V Tolerant, unlike nSS and the other SPI inputs to the CAM502. If the host outputs 5V logic signals, the level translation circuit of Figure 9 is required.

Figure 5 CAM502 connections, Type 2

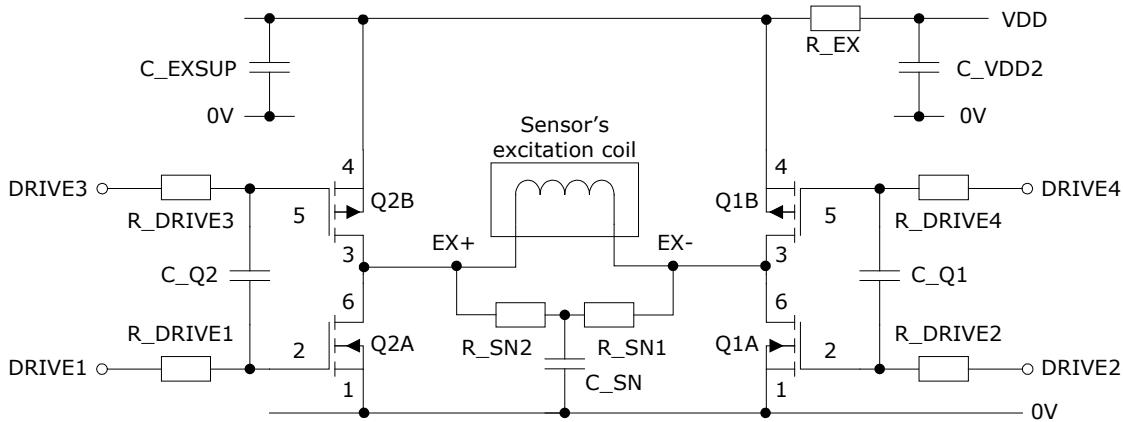

The CAM502 uses an external MOSFET "H" bridge to drive a Type 2 sensor's excitation coil. Figure 6 shows the excitation circuit. MOSFET pairs Q1 and Q2 are each available as a single miniature device, see Table 8. The gate drive circuit uses 2 resistors and 1 capacitor per side, and is designed to enable the CTU to drive the bridge output to a high impedance state. The resistors R\_DRIVE limit the operating speed of the MOSFETs, to minimise capacitively coupled emissions. The capacitors C\_Q1 and C\_Q2 prevent excessive shoot-through current during switching. The network R\_SN1, R\_SN2 and C\_SN absorb the energy in the excitation coil on the transition from low to high

impedance. The energy required for each pulse of excitation current is stored in C\_EXSUP. R\_EX limits the peak charging current.

Figure 6 Excitation Circuit, Type 2

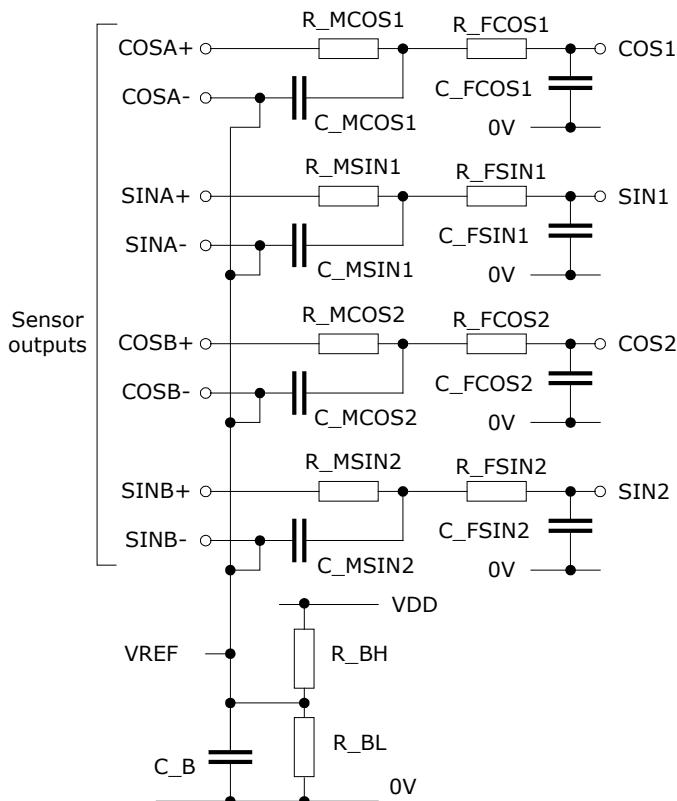

Figure 7 shows the components required for the sensor coil inputs to the CTU. Each of the 4 coil inputs has two stages of RC filtering formed by the components with prefix R\_F2, C\_F2, R\_F and C\_F. The reference voltage VREF is generated by the network R\_BH, R\_BL and CB. VREF should not be generated by other means.

Figure 7 Sensor coil connections, Type 2

### 3.2 Components Required, Type 2

Table 8 lists the component values and numbers required for the schematics of section 3.1. The filter components connected to the CTU's sensor 1 inputs are important for reproducibility, and the table includes two grades for them: A and B. Grade A yields the least system to system reproducibility error due to component differences. Grade B components are more cost effective. Grade A and B reproducibility error is compared in Table 9.

**Table 8 components required for a Type 2 sensor**

| Circuit Ref   | Value              | Tolerance |              | Number required |

|---------------|--------------------|-----------|--------------|-----------------|

|               |                    | Grade A   | Grade B      |                 |

| R_RESET1      | 10kΩ               |           | ±5%          | 1               |

| R_RESET2      | 470 Ω              |           | ±5%          | 1               |

| R_AVDD        | 10Ω                |           | ±5%          | 1               |

| R_DRIVE1/2    | 1.6kΩ              |           | ±5%          | 2               |

| R_DRIVE3/4    | 330Ω               |           | ±5%          | 2               |

| R_EX          | 1Ω                 |           | ±5%          | 1               |

| R_SN1/2       | 100Ω               |           | ±5%          | 2               |

| R_MCOS1/SIN1  | 100Ω               | ±0.1%     | ±1%          | 2               |

| R_MCOS2/SIN2  | 100Ω               |           | ±1%          | 2               |

| R_FCOS1/SIN1  | 1kΩ                | ±0.1%     | ±1%          | 2               |

| R_FCOS2/SIN2  | 1kΩ                |           | ±1%          | 2               |

| R_BH          | 15kΩ               |           | ±1%          | 1               |

| R_BL          | 10kΩ               |           | ±1%          | 1               |

| C_VDD         | 470nF              |           | ±10%         | 1               |

| C_AVDD        | 10µF, ESR < 3Ω     |           | ±20%         | 1               |

| C_CORE        | 10µF, ESR < 3Ω     |           | ±20%         | 1               |

| C_EXSUP       | 100µF, ESR < 100mΩ |           | -50% / +100% | 1               |

| C_VDD2        | 100µF, ESR < 100mΩ |           | -50% / +100% | 1               |

| C_RESET       | 100nF              |           | ±10%         | 1               |

| C_Q1/2        | 1nF                |           | ±10%         | 2               |

| C_SN          | 10nF               |           | ±10%         | 1               |

| C_MCOS/SIN1   | 2.2nF              | ±1%       | ±5%          | 2               |

| C_MCOS/SIN2   | 2.2nF              |           | ±5%          | 2               |

| C_FCOS/SIN1   | 220pF              | ±1%       | ±5%          | 2               |

| C_FCOS/SIN2   | 220pF              |           | ±5%          | 2               |

| C_B           | 470nF              |           | ±10%         | 1               |

| C_XIN, C_XOUT | 22pF (1)           |           | ±10%         | 2               |

| X1            | 8MHz               |           | ±30ppm       | 1               |

| Q1/2          | FDY4000CZ          |           |              | 2               |

Note (1): For crystal X1 requiring 12pF load capacitance

**Table 9 reproducibility error due to filter components**

| Grade | Reproducibility as % of Fine Pitch | Reproducibility in µm |                    |

|-------|------------------------------------|-----------------------|--------------------|

|       |                                    | Fine Pitch = 50mm     | Fine Pitch = 100mm |

| A     | ±0.03%                             | ±15µm                 | ±30µm              |

| B     | ±0.17%                             | ±85µm                 | ±170µm             |

## 4 Type 6 Sensor Application

Type 6 sensors are for the precise measurement of rotary position, and typically have a central opening for through-shaft operation. Please refer to sensor datasheets for more information.

### 4.1 Circuit Schematics, Type 6

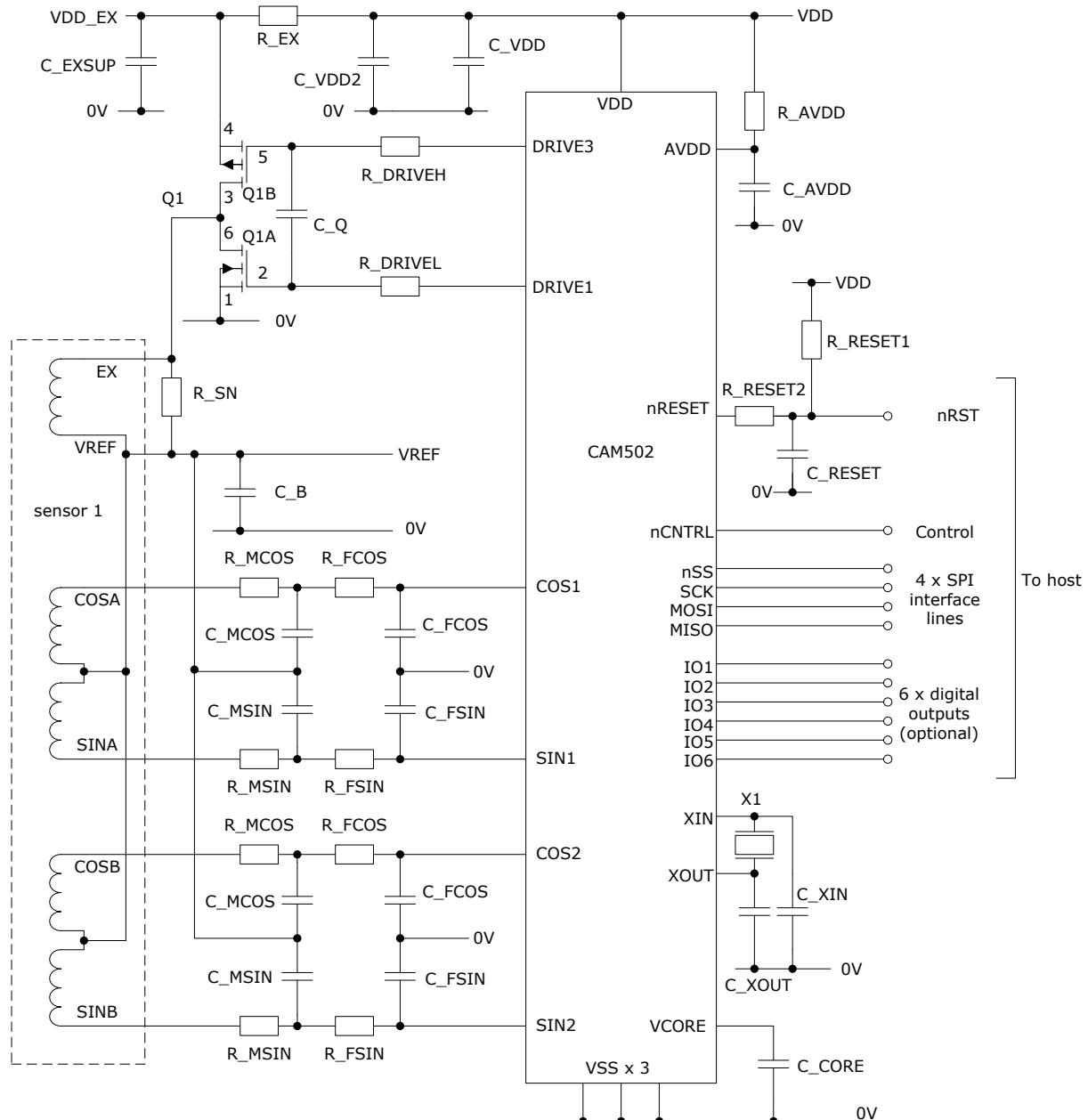

The circuit for connecting a Type 6 sensor to the CAM502 chip is shown in Figure 8 below. Component values are listed in Table 10.

VCORE is an external connection to an on-chip 2.5V regulator. This pin requires an external decoupling capacitor. It must not be connected to other circuitry.

AVDD is the analog supply input to the CAM502, and is used as a reference voltage. The values of R\_AVDD and C\_AVDD are important for the CAM502 to operate to full specification.

Figure 8 CAM502 connections, Type 6

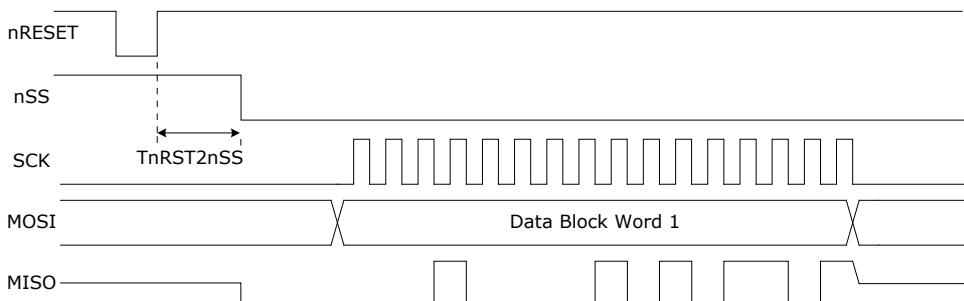

The CAM502's nRESET pin requires a series resistor R\_RESET2 for current limiting in the event of ESD, a pull-up resistor R\_RESET1 and a reset timing capacitor C\_RESET. The host may also perform a reset, by pulling the signal nRST low with an open drain output. Connecting the reset line in this way simplifies bootloader operation.

MISO is an open drain output, and requires a pull-up resistor of  $4.7\text{k}\Omega$  if this is not provided by the host.

The CAM502 uses an external crystal, X1, to derive precise timing.

The nCNTRL pin is for measurement control. It must be connected to nSS in pipeline mode with CONT=0 (section 7.3) so that measurements are synchronised to the host's acquisition of position data over the SPI interface. nCNTRL is not 5V Tolerant, unlike nSS and the other SPI inputs to the CAM502. If the host outputs 5V logic signals, the level translation circuit of Figure 9 is required.

**Figure 9 nCTRL level translation**

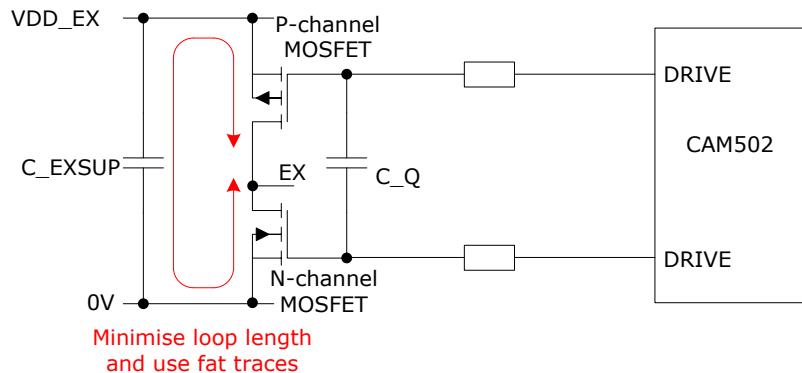

The CAM502 uses an external MOSFET half bridge to drive a Type 6 sensor's excitation coil. MOSFET pair Q1A and Q1B is available as a single miniature device. The gate drive circuit uses 2 resistors and 1 capacitor, and is designed to enable the CTU to drive the bridge output to a high impedance state. The resistors R\_DRIVE limit the operating speed of the MOSFETs, to minimise capacitively coupled emissions. The capacitor C\_Q prevents excessive shoot-through current during switching. R\_SN absorbs the energy in the excitation coil on the transition from low to high impedance. The energy required for each pulse of excitation current is stored in C\_EXSUP. R\_EX limits the peak charging current.

Each sensor's 4 coil inputs have two stages of RC filtering for immunity to external high frequency interference. The reference voltage VREF is generated by the switching action of the MOSFET driver. VREF should not be generated by other means.

## 4.2 Components Required, Type 6

Table 10 lists the component values and numbers required for the schematics of Figure 8.

**Table 10 components required for Type 6 sensor connection**

| Circuit Ref                     | Value          | Tolerance |         | Number required |

|---------------------------------|----------------|-----------|---------|-----------------|

|                                 |                | Grade A   | Grade B |                 |

| R_RESET1                        | 10kΩ           | ±5%       |         | 1               |

| R_RESET2                        | 470 Ω          | ±5%       |         | 1               |

| R_AVDD                          | 10Ω            | ±5%       |         | 1               |

| R_DRIVEL                        | 1.6kΩ          | ±5%       |         | 1               |

| R_DRIVEH                        | 330Ω           | ±5%       |         | 1               |

| R_EX                            | 1Ω             | ±5%       |         | 1               |

| R_SN                            | 1kΩ            | ±5%       |         | 1               |

| R_MCOS1/SIN1                    | 220Ω           | ±0.1%     | ±1%     | 2               |

| R_MCOS2/SIN2                    | 220Ω           | ±1%       |         | 2               |

| R_FCOS1/SIN1                    | 1kΩ            | ±0.1%     | ±1%     | 2               |

| R_FCOS2/SIN2                    | 1kΩ            | ±1%       |         | 2               |

| C_VDD                           | 470nF          | ±10%      |         | 1               |

| C_AVDD, C_CORE, C_EXSUP, C_VDD2 | 10μF, ESR < 3Ω | ±20%      |         | 4               |

| C_RESET                         | 100nF          | ±10%      |         | 1               |

| C_Q                             | 1nF            | ±10%      |         | 1               |

| C_MCOS/SIN1                     | 1nF            | ±1%       | ±5%     | 2               |

| C_MCOS/SIN2                     | 1nF            | ±5%       |         | 2               |

| C_FCOS/SIN1                     | 220pF          | ±1%       | ±5%     | 2               |

| C_FCOS/SIN2                     | 220pF          | ±5%       |         | 2               |

| C_B                             | 4.7μF          | ±10%      |         | 1               |

| C_XIN, C_XOUT                   | 22pF (1)       | ±10%      |         | 2               |

| X1                              | 8MHz           | ±30ppm    |         | 1               |

| Q1                              | FDY4000CZ      |           |         | 1               |

Note (1): For crystal X1 requiring 12pF load capacitance

The filter components connected to the CTU's sensor 1 inputs are important for reproducibility. The table above includes two grades for them: A and B. Grade A yields the least system to system reproducibility error due to component differences. Grade B components are slightly more cost effective. Grade A and B reproducibility error is compared in Table 11.

**Table 11 reproducibility error due to filter components, Type 6**

| Grade | Reproducibility due to filter components |                                 |                                |                                |

|-------|------------------------------------------|---------------------------------|--------------------------------|--------------------------------|

|       | As % of Fine Pitch<br>(Sin Length)       | Type 6.3<br>(Sin Length = 120°) | Type 6.5<br>(Sin Length = 72°) | Type 6.6<br>(Sin Length = 60°) |

| A     | ±0.03%                                   | ±0.036°                         | ±0.022°                        | ±0.018°                        |

| B     | ±0.17%                                   | ±0.20°                          | ±0.12°                         | ±0.10°                         |

### 4.3 Supply Current

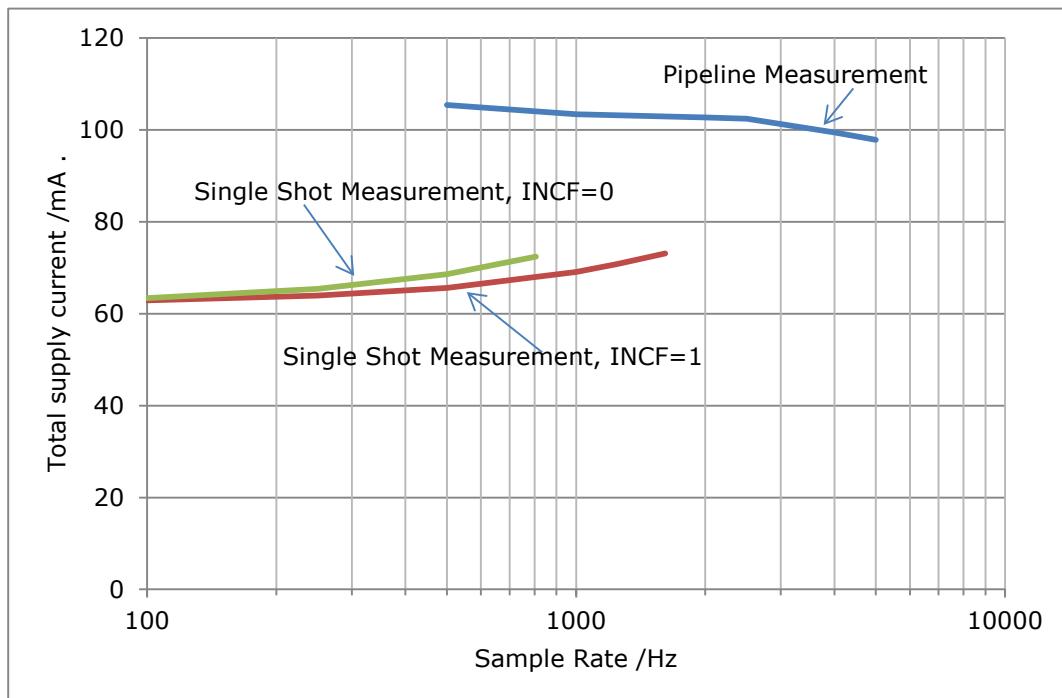

The CAM502's supply current depends on the rate at which it is sampling position, and the type of measurement. Pipeline measurement, described in section 9.7, yields the highest sample rates and the highest current consumption. Repeated single shot measurement (section 9.6) is suited to lower sample rates and yields lower current consumption. Single shot current consumption also depends on whether measurements are absolute (INCF=0) or incremental (INCF=1), see section 9.8.

Figure 10 is a graph of supply current against sample rate for the different modes, operating at a supply voltage of 3.3V. Figures include both the CAM502 supply current and the current required for the excitation circuit.

Figure 10 Supply current as a function of sample rate, at 3.3V

### 4.4 Noise Free Resolution

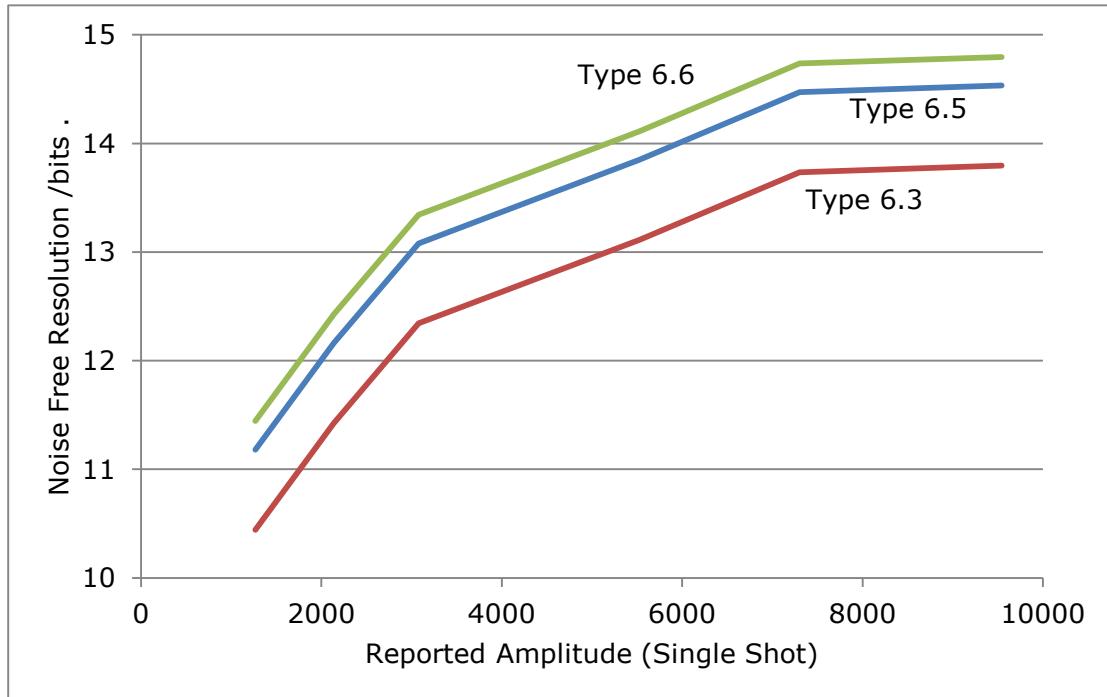

Position resolution is not limited by the number of bits reported over the SPI interface ( $\geq 18$  bits for a Type 6 sensor). A more useful measure of resolution is Noise Free Resolution. This describes how many different positions the CAM204 can distinguish, considering the random noise present in the lower bits of its output. It is generally a more useful measure than interface resolution for a system having excess interface resolution.

The random noise present in the CTU's reported measurements can be considered Gaussian (well behaved noise). There are two general measures of Random Noise, Peak to Peak Noise and Standard Deviation. Defining Peak to Peak Noise such that it encompasses 99.9% of samples (100% is physically impossible due to the statistical nature of noise) yields the following relationship:

$$\text{Peak To Peak Position Noise} = 6.6 \times \text{Standard Deviation}$$

**Equation 1**

Another common measure of noise used in encoders is Noise Free Resolution, which is related to Peak to Peak Noise as follows:

$$\text{Noise Free Resolution} = \log_2 \left( \frac{360^\circ}{\text{Peak to Peak Position Noise}} \right)$$

**Equation 2**

Noise Free Resolution depends on the Amplitude reported by the CAM502, which is a function of gap from sensor to target and their metal environment. Reported Amplitude can be established from the relevant sensor datasheet, or by experiment. Noise Free Resolution is also a function of sensor Subtype, with sensors having a higher Subtype number (more fine track sinusoidal periods) delivering the better performance.

Figure 11 shows the expected Noise Free Resolution as a function of Reported Amplitude for each Subtype, for Single Shot measurement (section 9.6).

**Figure 11 Noise Free Resolution, Type 6 sensors, Single Shot measurement**

Pipeline Measurement (section 9.7) is used for higher sample rates than Single Shot. Operating in this mode, Reported Amplitude is approximately 20% higher than Single Shot, while Noise Free Resolution is typically 0.4 bits lower.

Noise Free Resolution can be improved by averaging raw samples from a CTU chip. Averaging  $2N$  samples increases Noise Free Resolution by  $N/2$  bits. So averaging 4 samples ( $N=2$ ) improves Noise Free Resolution by 1 bit, and averaging 16 ( $N=4$ ) samples improves Noise Free Resolution by 2 bits. Measurements of Linearity Error and Offset Error are separated from Random Noise by averaging in this way. Noise Free Resolution may also be improved by configuring the CAM502 to digitally filter results, as described in section 9.11.

## 5 Circuit Layout

This section contains recommendations for the PCB layout of the CAM502 circuitry, and applies to both Type 2 sensor circuitry (section 3) and Type 6 (section 4).

### 5.1 Ground Plane and Capacitor Connections

It is recommended to use a PCB with at least 4 layers, one of which should be a solid ground plane below the CAM502. Conductors carrying signals not associated with the CAM502 chip should not be placed between the CAM502 chip and ground plane.

Connections from the CAM502's VSS pins to the ground plane must be made with vias placed close to the chip. Capacitors C\_VDD, C\_AVDD, C\_CORE, C\_XIN and C\_XOUT must be kept close to the chip with short distances to ground connections, as illustrated in Figure 12.

**Figure 12 Ground plane vias and capacitors close to the CAM502 chip**

It is also important to keep the capacitors used for sensor filtering close to the CAM502 chip, as detailed in the next section.

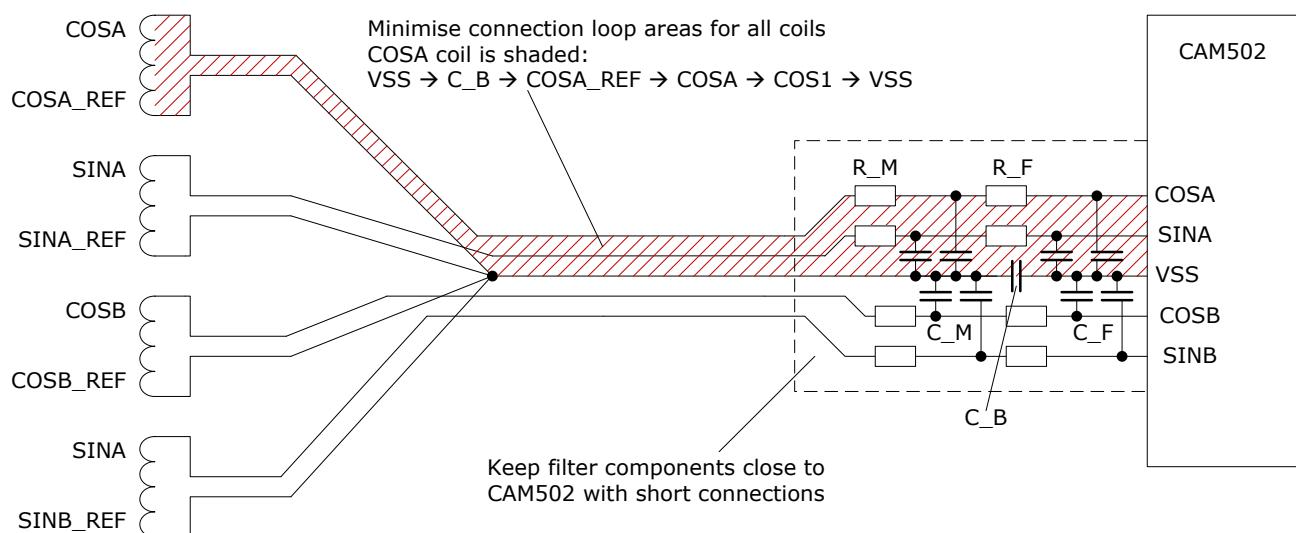

## 5.2 Sensor Coil Connections to CAM502

Figure 13 illustrates connections between sensor coils and the CAM502 circuit, including its filter components. When a sensor coil is connected to the CTU circuit, the traces and/or wires forming the connection make a loop. The loop formed by the COSA coil connections is shaded as an example.

**Figure 13 Sensor coil connections to CAM502**

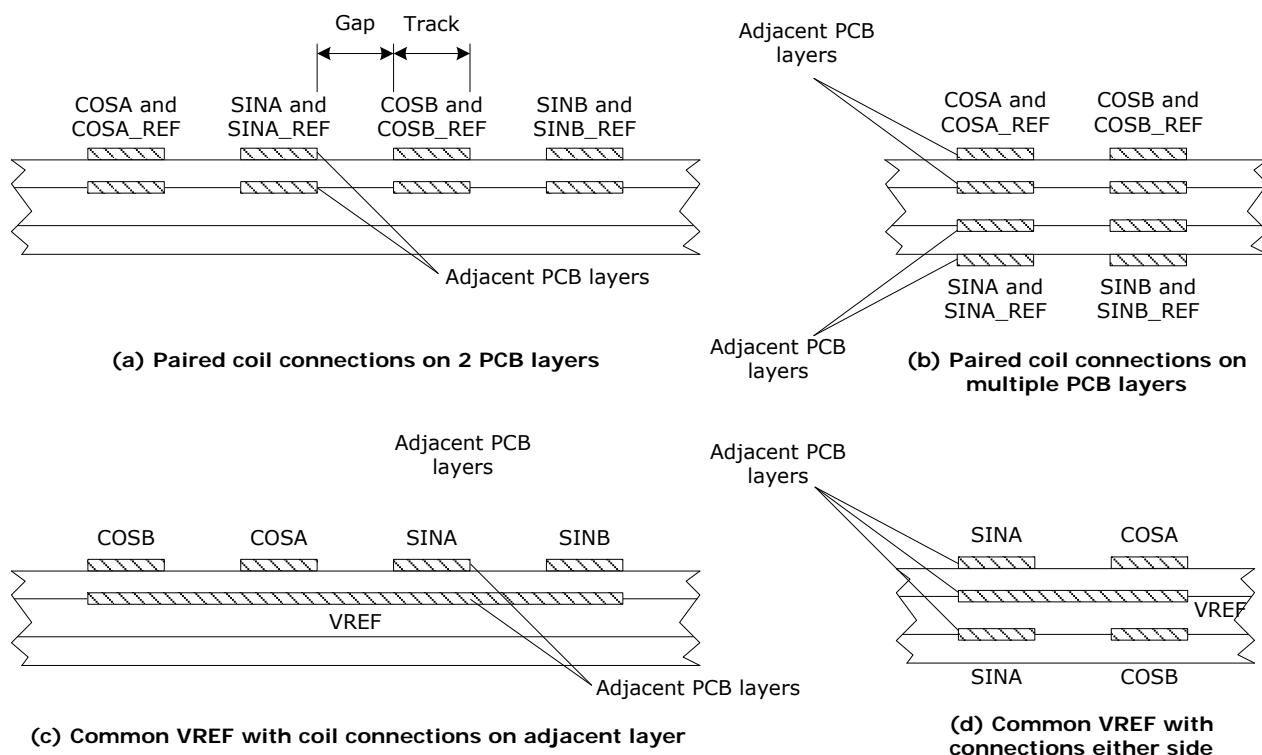

The loop area for each of the sensor coils must be minimised, in order to minimise coupling to the target and/or any AC magnetic interference. Wires used for connection must be run in a tight bundle, on adjacent conductors in a ribbon cable or twisted. Conductors on a PCB should be arranged in coil pairs as in Figure 14 (a) or (b), or adjacent to a common VREF conductor as in Figure 14 (c) or (d).

**Figure 14 PCB conductor arrangements for sensor coils**

Track and Gap figures should be minimised, providing connection resistance does not fall below  $5\Omega$ , or below  $1\Omega$  for a VREF connection that is common to two or more coils.

### 5.3 Excitation Circuit and Coil Connections

The CAM502 chip drives the gates of external MOSFET pair(s), which in turn drive current into the excitation coil to energise the resonator inside the target. Type 2 circuitry uses a H-bridge circuit employing two MOSFET pairs (Figure 6), while Type 6 circuitry uses a single MOSFET pair (Figure 8).

To keep the circuit efficient and to minimise emissions, the excitation circuit's decoupling capacitor  $C_{EXSUP}$  must be kept close to the MOSFET pair(s), and should be connected to them with fat traces and the minimum of trace lengths.

**Figure 15** Excitation circuit layout

Each capacitor  $C_Q$  should be located near the MOSFET it is connected to.

Excitation coil connections must be made with a minimum of loop area, in a similar way to sensor coil connections.

The excitation coil connecting track widths should preferably be wide to minimise resistance. A loop resistance of less than  $0.5\Omega$  is preferable. PCBs with 1oz copper (34 $\mu$ m thick) have a surface resistivity of 0.5m $\Omega$ /square, so connections can be up to 1000 squares long. Table 12 shows how the minimum width of each trace in the pair of traces connecting the excitation coil varies with length.

Sensor and excitation traces may be run adjacent to one another. Type 6 sensors share a common VREF for both sensor and excitation coil, and the EX connection may be added to one side of the parallel connections shown in Figure 14 (c) or (d). It is more important to minimise sensor coil connection area than excitation, in any case there is a conflict between the two.

**Table 12** Minimum conductor widths on 1oz (34 $\mu$ m) PCB for  $\leq 0.5\Omega$  loop resistance

| Length of excitation conductor pair | Minimum conductor width |

|-------------------------------------|-------------------------|

| 100mm                               | 0.2mm                   |

| 200mm                               | 0.4mm                   |

| 400mm                               | 0.8mm                   |

| 800mm                               | 1.6mm                   |

## 6 Resonator Detection

The CAM502 chip is connected to one or more sensors, and detects the position of inductively coupled resonators inside targets coupled to each sensor. For each measurement it first performs an excitation burst to power the resonator, then switches this off and detects the EMFs induced by the resonator in the sensor coils. Please refer to a sensor's datasheet for more details on its principle of operation.

The CAM502 first detects each resonator using a *search* operation with a *broadband* excitation burst to determine its frequency. Subsequent measurements are *narrowband*, designed to maximise resonator EMFs, unless or until the target goes out of range. Each measurement the CAM502 chip updates its estimate of resonator frequency, so that the next excitation burst is at the optimum frequency. That way the CAM502 corrects for changes in resonator frequency due to drift and any changes in metal environment, so that excitation is always at the optimum frequency.

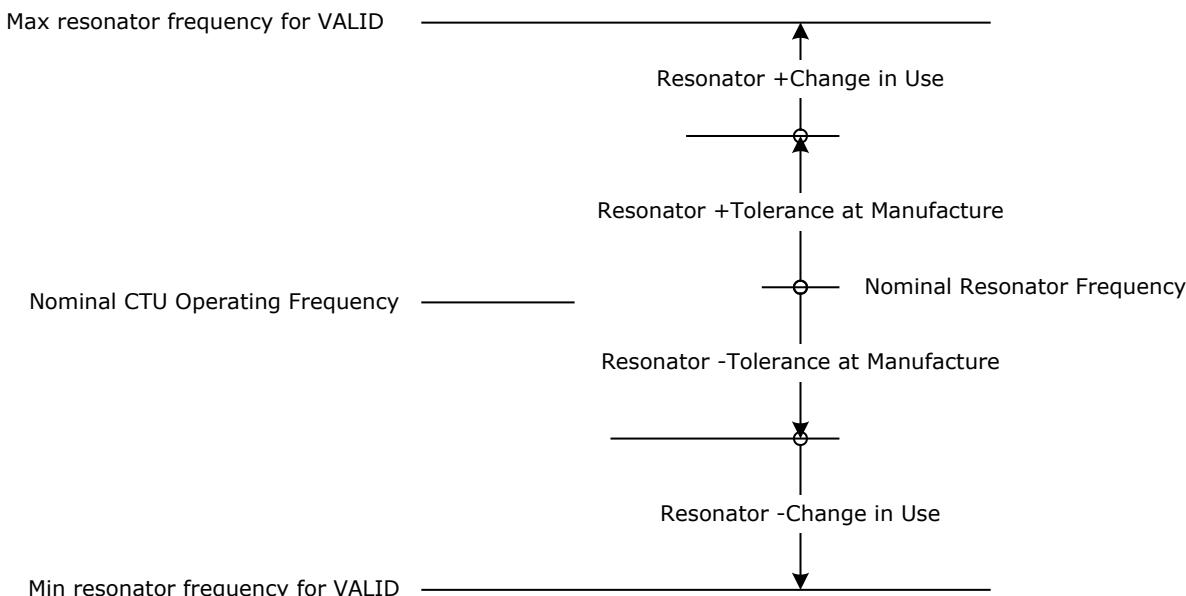

The CAM502 CTU's Nominal Operating Frequency (Table 13) is under crystal control. For diagnostic purposes it reports resonator frequency in the results registers. This Reported Frequency is in Hz relative to the CTU's Nominal Operating Frequency.

**Table 13** resonator detection parameters

| Item                                  | Min       | Typ       | Max       | Comments                                |

|---------------------------------------|-----------|-----------|-----------|-----------------------------------------|

| CTU Nominal Operating Frequency       | 185.99kHz | 186.01kHz | 186.03kHz |                                         |

| Min resonator frequency for VALID     |           |           | 172.2kHz  |                                         |

| Max resonator frequency for VALID     | 199.8kHz  |           |           |                                         |

| Resolution of Reported Frequency      |           | 465Hz     |           |                                         |

| Resonator Q-factor                    | 60        |           | 150       |                                         |

| Minimum Amplitude for VALID           | 1024      |           | 1100      | Measured once VALID in single shot mode |

| Rate of change of resonator frequency |           |           | 1kHz/ms   | For VALID position measurement          |

The CAM502 detects resonator frequency to yield a VALID position measurement result across a wide range of frequencies, from the minimum to the maximum values shown above. This wide range allows resonators to be manufactured with relaxed frequency tolerance. It also allows for additional margin for positive and negative frequency changes in use, for example due to the presence nearby metals. These allowances are illustrated in Figure 16.

**Figure 16** Illustration of frequency tolerance budgets

## 7 SPI Hardware

### 7.1 Overview

This section describes how data is written to, and read back from, the CAM502 CTU, over its SPI interface. Each read or read-write operation accesses one or more of the CTU's internal registers.

For communication with a host system, the CAM502 CTU is always an SPI slave. All communication is initiated by the host.

### 7.2 Data Transfer Method

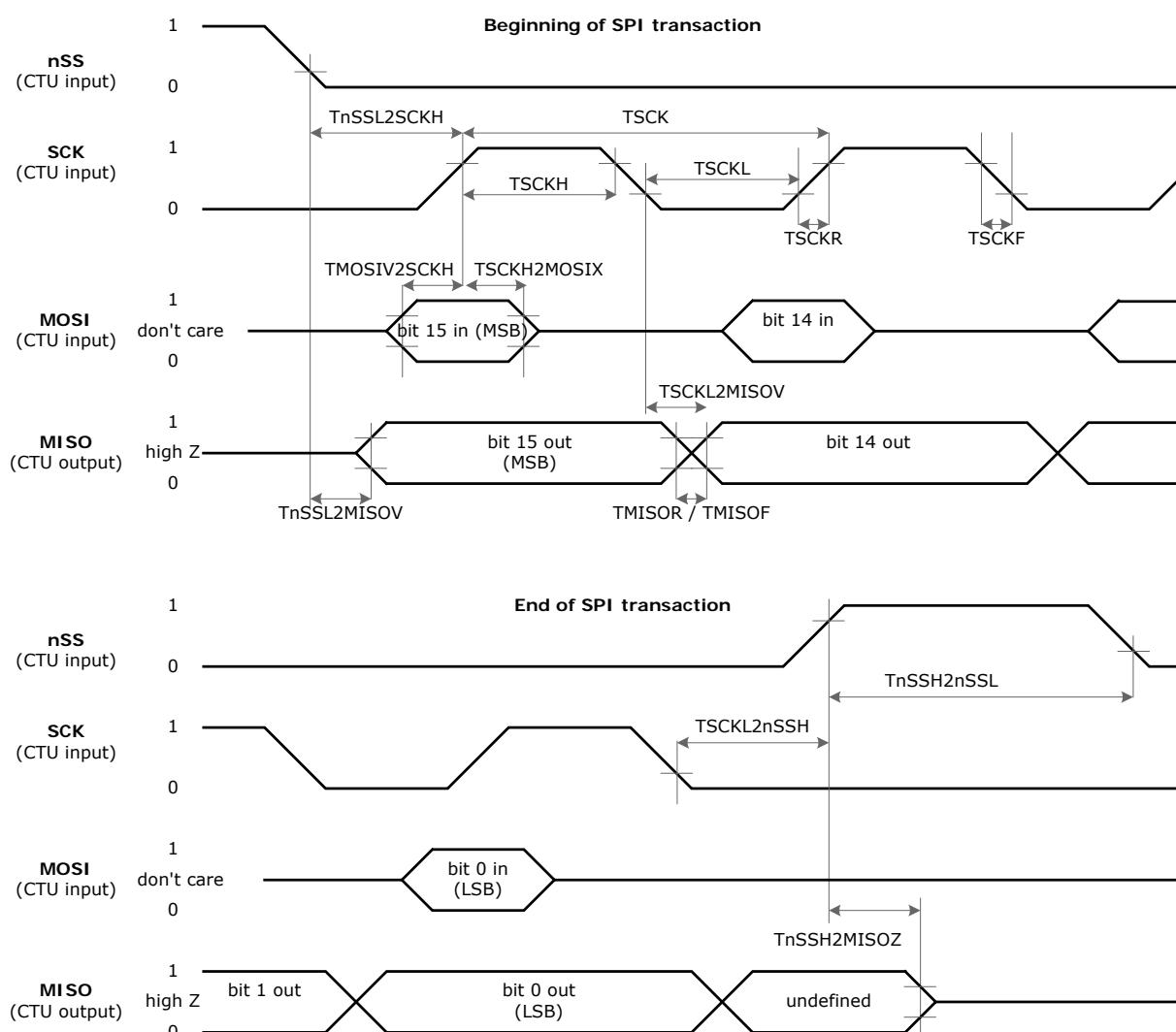

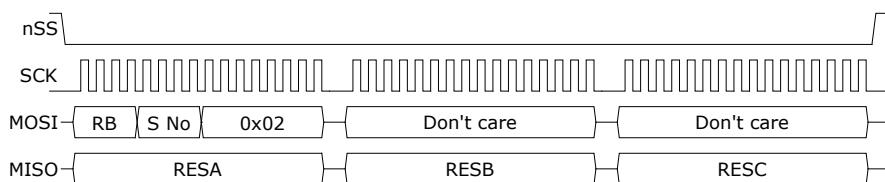

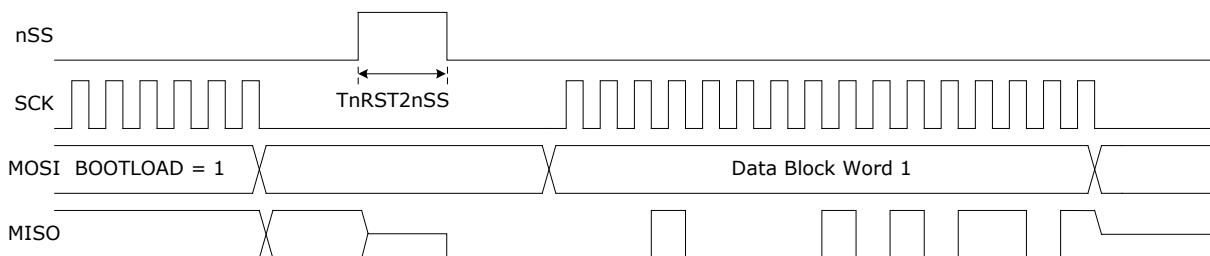

The CAM502 CTU always operates as an SPI slave device. The host device starts a data transfer by driving nSS low. It sends data to the CAM502 with the MOSI line, and provides the CAM502 with a serial clock line SCK. The CAM502 detects each MOSI bit on the rising edge of SCK. The CTU sends data back to the host with the MISO line. Bits change state on the falling edge of SCK, and the host should detect the state of MISO on each rising edge. This is commonly referred to as SPI Mode 0. The beginning and end of an SPI transaction is illustrated in Figure 17.

All SPI transactions MUST be bounded by the Slave Select (nSS) line being driven low at their start and being driven high at their end. The SPI interface will not function if nSS is tied permanently low.

Figure 17 SPI Data Transfer

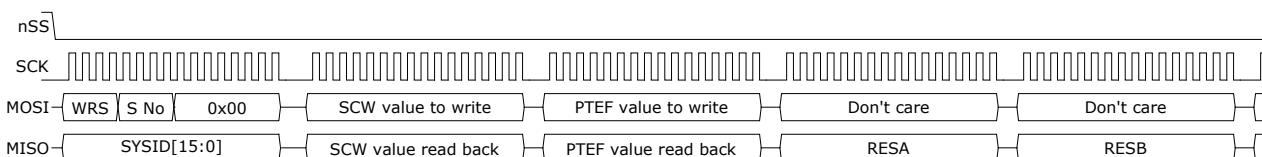

### 7.3 Standard SPI Format Register Access

The host operates the CAM502 CTU by writing to and reading from registers. There are a number of registers with different functions. Each register is 16 bits wide, and has its own 12 bit address.

The host must start each SPI transaction by clocking out 4 ACS bits field followed by 12 address bits on MOSI. The function of the ACS bits is defined in Table 14. The ACS bits define whether the current SPI transaction reads from registers (*Read*), or writes and reads data (*Write Read*). The ACS bits also define the format of the next SPI transaction, which may either be *Standard SPI Format* or *Burst SPI Format*. This section describes Standard SPI Format, and section 7.4 describes Burst SPI Format.

**Table 14 ACS bits definition**

| ACS[3:0]  | Abbreviation | Access type, this SPI transaction | Format of next SPI transaction |

|-----------|--------------|-----------------------------------|--------------------------------|

| 0x0       | RS           | Read                              | Standard SPI Format            |

| 0x1       | RB           | Read                              | Burst SPI Format               |

| 0x2...0xD |              | Reserved, do not use              |                                |

| 0xE       | WRB          | Write Read                        | Burst SPI Format               |

| 0xF       | WRS          | Write Read                        | Standard SPI Format            |

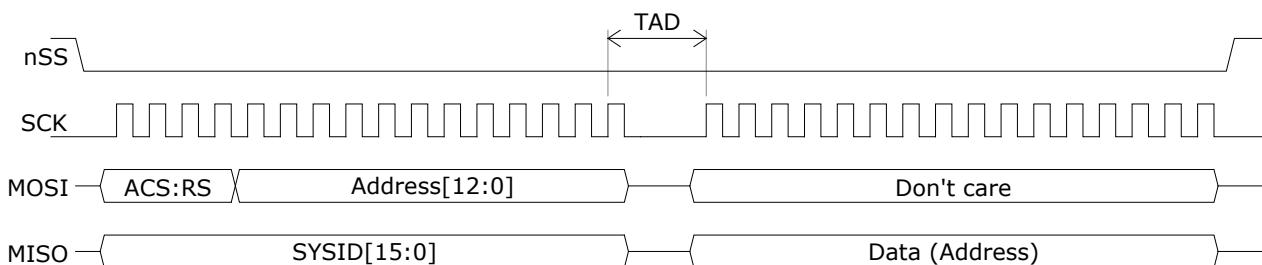

When the host requests a Read in Standard SPI Format, the next 16 bits clocked out of MISO are the data contained in the register at the specified address. The CAM502 ignores the state of MOSI during data transfer. This transaction is illustrated in Figure 18.

**Figure 18 Standard Read, single register**

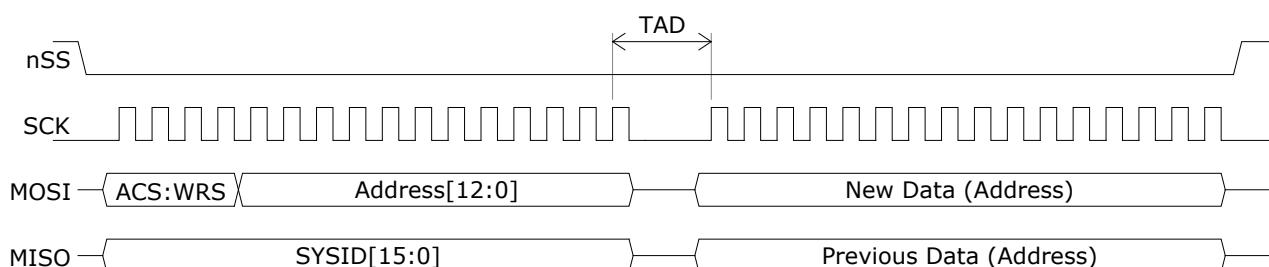

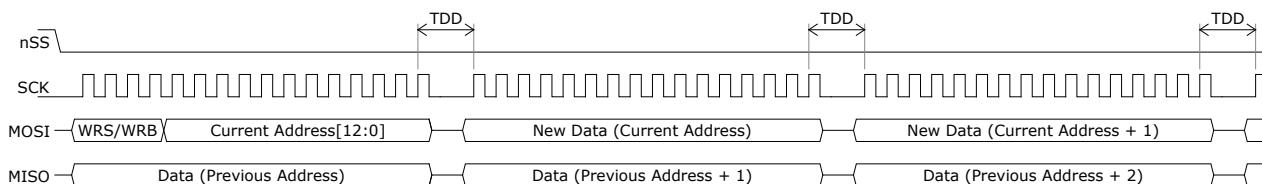

A Write Read operation is similar, except the host also updates the register contents with the new data that the host clocks out of the MOSI line after the address. The data returned on the MISO line is the register contents before the update. This transaction is illustrated in Figure 19.

**Figure 19 Standard Write Read, single register**

For both of these Standard SPI Format operations, a time TAD is required between the rising edge of SCK that clocks in the last address bit and the rising edge of SCK that clocks out the first data bit, illustrated in Figure 18 and Figure 19 above. TAD allows the CAM502 time to load its SPI transmit buffer with data from the correct address.

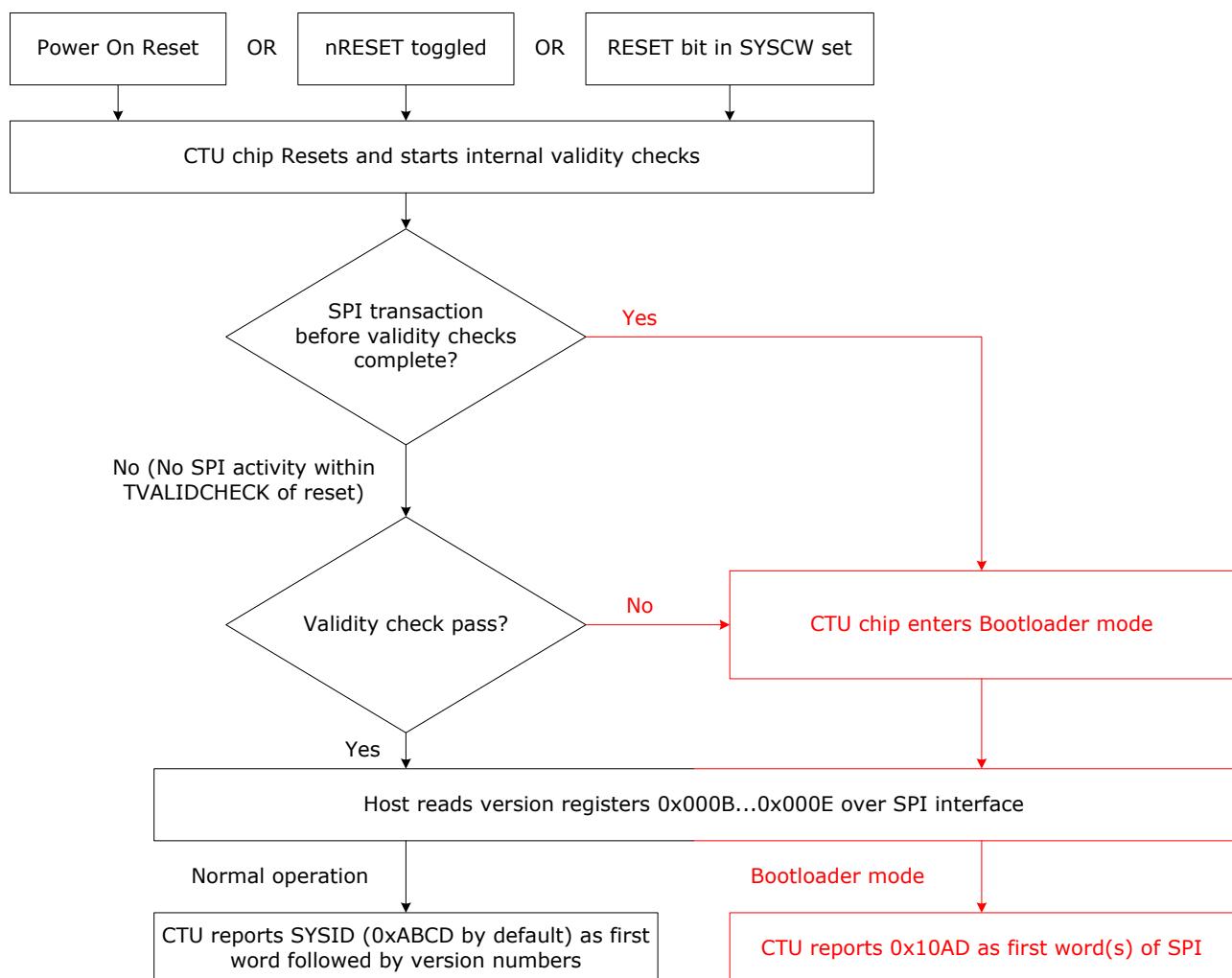

The CTU outputs the contents of its SYSID register as the first word of each standard SPI transaction. This defaults to 0xABCD, and may be changed by the host, please see section 8.8. Other values are possible when operating in Bootloader mode, or as a result of errors. Please see Table 27. It is recommended that the host checks the value read back against the expected value as a test for SPI communication integrity.

If the host attempts to access a reserved or unimplemented address, incoming data will be discarded and the state of MISO is undefined.

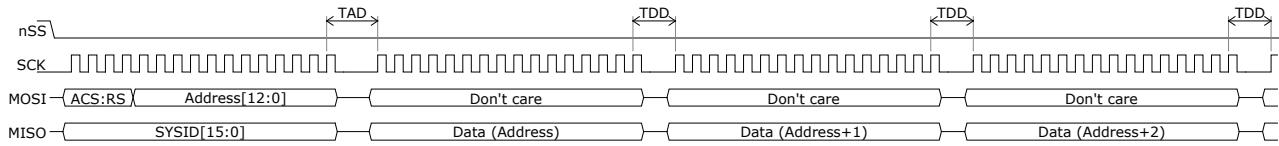

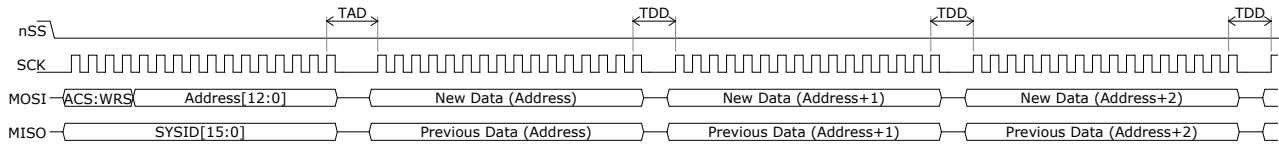

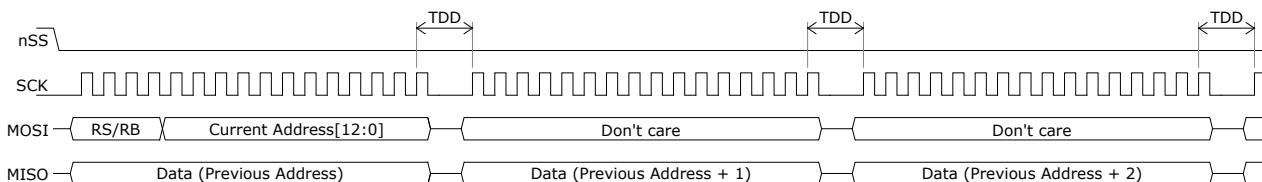

Instead of accessing a single register, the host may access a set of consecutive registers by extending the SPI transaction as illustrated in Figure 20 and Figure 21. Data is transferred one register at a time, starting at the first specified address. Registers are arranged in blocks dedicated to system functions, and to each sensor connected, distinguished by the upper 4 bits of the address. Multiple register access must not span different blocks.

It is not essential to transfer complete 16 bit words into the CAM502. However it is recommended, since data from any incomplete word will be discarded.

There is a minimum time TDD required between adjacent data words, to allow the CAM502 time to load the SPI transmit buffer with data for the next address. This is measured between the last rising edge of SCK of one word and the first rising edge of SCK of the next. At lower bit rates, when TSCK is greater than or equal to TDD, the SCK clock may run continuously with no additional delays. TDD is illustrated in Figure 20 and Figure 21, and specified in Table 15.

**Figure 20 Multiple register access, Read**

**Figure 21 Multiple register access, Write Read**

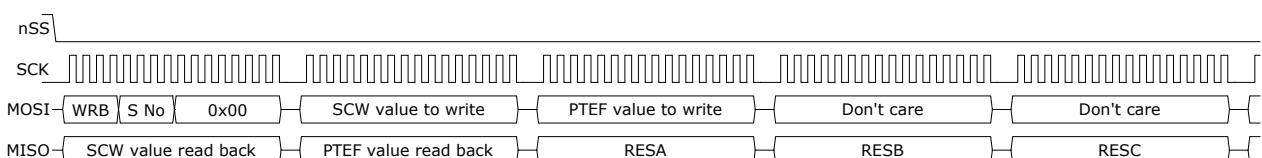

## 7.4 Burst SPI Format Register Access

The host may request that the next SPI transaction has Burst SPI Format using the appropriate ACS bit settings listed in Table 14. Burst SPI Format has the following features:

- Data is read from the address specified by the host in the *previous* SPI transaction.

- Data is written to the address specified by the host in the *current* SPI transaction, like Standard SPI Format.

- The host transmits data immediately, and does not prefix data with the SYSID register.

- The time delay TAD is not required between Address and Data, because the CAM502 loads its SPI buffer before the next SPI transaction. The shorter time TDD is required between all words instead.

- The maximum value of TnSSL2MISOV and the minimum value of TnSSL2SCKH are increased slightly to allow the CAM502 time to set up the first SPI word to transmit to the host (Table 15). The increase is small compared to the overall decrease in SPI transaction time due to the elimination of TAD, so that SPI transaction times are reduced significantly. Please see Table 16 for examples.

These features are intended to speed up data access for systems requiring low latency operation, particularly when repeated and rapid access to a sensor's results registers is required.

Figure 22 and Figure 23 both illustrate SPI transactions with Burst SPI Format; the previous ACS bits must have been either RB or WRB. The first word out of MISO is data from the register location whose address was specified in this previous SPI transaction, and it is followed by data from the following addresses.

**Figure 22 Burst SPI Format, Read**

**Figure 23 Burst SPI Format, Write Read**

Figure 22 illustrates the case when the current SPI transaction is a Read. The ACS bits can be set to either RS (Read, next SPI transaction Standard SPI Format) or RB (Read, next SPI transaction also Burst SPI Format).

Figure 23 illustrates the case when the current SPI transaction is a Write Read. It can either be a WRS (Write Read, next SPI transaction Standard SPI Format) or WRB (Write Read, next SPI transaction also Burst SPI Format). In both cases, the host should transmit data after the address bits. This is written to the register address specified in the current SPI transaction. Note that a Burst SPI Format Write Read allows the host to read from one more register than it writes to.

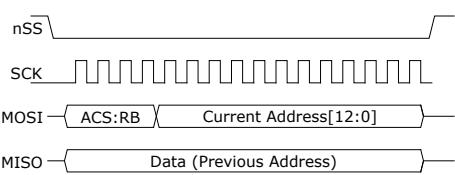

An additional feature of Burst SPI Format is that it allows the host to Read CAM502 registers with a single 16-bit word SPI transaction, as illustrated in Figure 24.

**Figure 24 Burst SPI Format, Read from one register**

## 7.5 Interface Timing Specifications

Table 15 Interface timing specifications

| Parameter   | Description                                                                                  |                     | Min | Typ | Max | Units |

|-------------|----------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|-------|

| TVALIDCHECK | Time for CTU internal validity checks following reset                                        |                     | 5   | -   | 12  | ms    |

| TSCKL       | SCK Input Low Time                                                                           |                     | 30  | -   | -   | ns    |

| TSCKH       | SCK Input High Time                                                                          |                     | 30  | -   | -   | ns    |

| TSCK        | SCK clock period                                                                             |                     | 100 | -   | -   | ns    |

| TSCKR       | SCK Input Rise Time                                                                          |                     | -   | 10  | 25  | ns    |

| TSCKF       | SCK Input Fall Time                                                                          |                     | -   | 10  | 25  | ns    |

| TMISOR      | MISO Rise Time (50pF load)                                                                   |                     | -   | -   | 25  | ns    |

| TMISOF      | MISO Fall Time (50pF load)                                                                   |                     | -   | -   | 25  | ns    |

| TMOSIV2SCKH | MOSI Setup Time                                                                              |                     | 30  | -   | -   | ns    |

| TSCKH2MOSIX | MOSI Hold Time                                                                               |                     | 30  | -   | -   | ns    |

| TSCKL2MISOV | MISO valid after SCK edge                                                                    |                     | -   | -   | 30  | ns    |

| TnSSL2MISOV | MISO valid after nSS edge                                                                    | Standard SPI Format | -   | -   | 100 | ns    |

|             |                                                                                              | Burst SPI Format    | -   | -   | 230 | ns    |

| TnSSL2SCKH  | nSS low to SCK edge                                                                          | Standard SPI Format | 120 | -   | -   | ns    |

|             |                                                                                              | Burst SPI Format    | 250 | -   | -   | ns    |

| TSCKL2nSSH  | Last SCK edge to nSS high                                                                    |                     | 100 | -   | -   | ns    |

| TnSSH2MISOZ | nSS high to MISO high Z                                                                      |                     | 10  | -   | 50  | ns    |

| TAD         | Address end to first data,<br>Standard SPI Format only                                       | CONT=0              | 5   | -   | -   | μs    |

|             |                                                                                              | CONT=1              | 7   | -   | -   | μs    |

| TDD         | Delay between data words                                                                     |                     | 250 | -   | -   | ns    |

| TnSSH2nSSL  | nSS high time following read of register(s), excluding pipeline measurement                  |                     | 6   | -   | -   | μs    |

|             | nSS high time following write to register(s) controlling IO, LED or DAC configuration        |                     | 200 | -   | -   | μs    |

|             | nSS high time during pipeline measurement                                                    |                     | 174 |     |     | μs    |

|             | nSS high time, any other SPI transaction                                                     |                     | 40  | -   | -   | μs    |

| TnSSH2IOch  | Time to clear an IO by clearing SIF or PTF bits                                              |                     | -   | -   | 40  | μs    |

|             | Time to change an IO following write to register(s) controlling IO, LED or DAC configuration |                     | -   | -   | 200 | μs    |

## 7.6 Minimum SPI Transaction Times

The time taken for any SPI transaction depends on the actual host timings used and the number of registers accessed. Table 16 provides examples of the minimum SPI transaction time, measured from nSS low edge to high, and based on minimum interface timings taken from Table 15.

When operating in Continuous mode with CONT=1, and using standard SPI transactions, a larger value of TAD is required, as described in section 9.10.

**Table 16 minimum SPI transaction times**

| Registers accessed     | Standard SPI Format,<br>CONT=0 | Standard SPI Format,<br>CONT=1 | Burst SPI Format |

|------------------------|--------------------------------|--------------------------------|------------------|

| SCW, PTEF, RESA...RESE | 20.5 $\mu$ s                   | 22.5 $\mu$ s                   | 15.9 $\mu$ s     |

| RESA, RESB, RESC       | 12.0 $\mu$ s                   | 14.0 $\mu$ s                   | 5.4 $\mu$ s      |

## 8 Register Description

The host configures and controls the CAM502 CTU chip by writing to its internal registers. It obtains status and measurement results by reading back from internal registers. This section describes the function of each of the CTU's registers.

Reading and writing to registers is done over the SPI interface, using the procedures described in section 7. Section 9 describes how to control the CTU to perform sensor position measurements, and how to configure the function of the CTU's IO pins.

The CTU's register map is arranged in distinct sections: a system control section and one section for each sensor. The arrangement is illustrated in Figure 25. The register map shows a number of registers whose functions are not implemented in the CAM502, for compatibility with other CTU chips. For example the PTEF register controls position trigger behaviour in the CAM204 chip, but is not used in the CAM502.

The register map has been arranged to reduce SPI overheads once the whole system has been initialised following a reset. Once initialised, the host system will normally only need to access a small contiguous block of registers to control each sensor, which can be performed within a single SPI transaction.

| Address | Description                  | Register | 15           | 14           | 13           | 12                  | 11   | 10           | 9            | 8     | 7    | 6    | 5    | 4           | 3    | 2    | 1    | 0    |

|---------|------------------------------|----------|--------------|--------------|--------------|---------------------|------|--------------|--------------|-------|------|------|------|-------------|------|------|------|------|

| 0x 1 1F | Pos Trig Position 8          | PTP8     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 1E | Pos Trig Position 7          | PTP7     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 1D | Pos Trig Position 6          | PTP6     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 1C | Pos Trig Position 5          | PTP5     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 1B | Pos Trig Position 4          | PTP4     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 1A | Pos Trig Position 3          | PTP3     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 19 | Pos Trig Position 2          | PTP2     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 18 | Pos Trig Position 1          | PTP1     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 17 | PT Auto-Clear & Hysteresis   | PTAH     | PTAUTOCLR    |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

|         |                              |          |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 16 | Position Trigger 8&7 Control | PTC87    | PT8ACT [1:0] | PT8DIR [1:0] |              | PT8MAP [3:0]        |      | PT7ACT [1:0] | PT7DIR [1:0] |       |      |      |      |             |      |      |      |      |

| 0x 1 15 | Position Trigger 6&5 Control | PTC65    | PT6ACT [1:0] | PT6DIR [1:0] |              | PT6MAP [3:0]        |      | PT5ACT [1:0] | PT5DIR [1:0] |       |      |      |      |             |      |      |      |      |

| 0x 1 14 | Position Trigger 4&3 Control | PTC43    | PT4ACT [1:0] | PT4DIR [1:0] |              | PT4MAP [3:0]        |      | PT3ACT [1:0] | PT3DIR [1:0] |       |      |      |      |             |      |      |      |      |

| 0x 1 13 | Position Trigger 2&1 Control | PTC21    | PT2ACT [1:0] | PT2DIR [1:0] |              | PT2MAP [3:0]        |      | PT1ACT [1:0] | PT1DIR [1:0] |       |      |      |      |             |      |      |      |      |

| 0x 1 12 | Sample Indicator Control     | SIC      |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 11 | Sensor Type                  | STYPE    |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 10 | DAC Control Word             | DACCW    |              |              |              | DACNV [15:8]        |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 0F | DAC Limit Y                  | DACLIMY  |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 0E | DAC Limit X                  | DACLIMX  |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 0D | DAC Position D               | DACPOSD  |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 0C | DAC Position C               | DACPOS C |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 0B | DAC Position B               | DACPOS B |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 0A | DAC Position A               | DACPOS A |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 09 | LED Control Word             | LEDCW    |              |              |              | LEDTHRESHOLD [11:0] |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 08 | Sensor Constants             | CONST    | -            | -            | -            | -                   | -    | -            | -            | -     | -    |      |      | FCSEL [3:0] |      |      |      |      |

| 0x 1 07 | Result Register F            | RESF     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 06 | Result Register E            | RESE     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 05 | Result Register D            | RESD     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 04 | Result Register C            | RESC     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 03 | Result Register B            | RESB     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 02 | Result Register A            | RESA     |              |              |              |                     |      |              |              |       |      |      |      |             |      |      |      |      |

| 0x 1 01 | Pos Trig Enables/Flags       | PTEF     | PT8E         | PT7E         | PT6E         | PT5E                | PT4E | PT3E         | PT2E         | TPT1E | PT8F | PT7F | PT6F | PT5F        | PT4F | PT3F | PT2F | PT1F |

| 0x 1 00 | Sensor Control Word          | SCW      |              |              | SENSOR [3:0] |                     | PIE  | PIF          | INCE         | INCF  | SIE  | SIF  | NEW  | VALID       |      | TRIG | CONT | GO   |

|         |                            |         |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

|---------|----------------------------|---------|--------|----------|------|---------|--------|--------|--------|--------|--------|--------|-------------|--------|--------|-----------------|--------|--------|

| 0x 0 0F | Device ID                  | SYSID   |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 0E | System Version Number      | SYSVER  |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 0D | Bootloader Version Number  | BOOTVER |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 0C | Save Key                   | SAVEKEY |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 0B | (Reserved)                 |         |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 0A | (Reserved)                 |         |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 09 | (Reserved)                 |         |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 08 | (Reserved)                 |         |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 07 | (Reserved)                 |         |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 06 | (Reserved)                 |         |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 05 | (Reserved)                 |         |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 04 | (Reserved)                 |         |        |          |      |         |        |        |        |        |        |        |             |        |        |                 |        |        |

| 0x 0 03 | System DAC Register        | SYSDAC  | DACCAL | -        | -    | -       | -      | -      | -      | CPOL   | CPHA   |        |             |        |        | DACFORMAT [2:0] | DACSON |        |

| 0x 0 02 | IO Pin Types               | SYSIO   | -      | -        | -    | -       | INT6AH | INT6DO | INT5AH | INT5DO | INT4AH | INT4DO | INT3AH      | INT3DO | INT2AH | INT2DO          | INT1AH | INT1DO |

| 0x 0 01 | Continuous Sample Interval | SYSI    |        |          |      |         |        |        |        |        |        |        | SYSI [15:0] |        |        |                 |        |        |

| 0x 0 00 | System Control Word        | SYSCW   | RESET  | BOOTLOAD | SAVE | FACTORY |        |        |        |        |        |        |             |        |        |                 |        | PWRDN  |

Read Only

Read / Write

Read / Write to 0

Figure 25 Register map

## 8.1 SYSCW: System Control Word

| SYSCW  | 15    | 14       | 13    | 12      | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|----------|-------|---------|----|----|---|---|---|---|---|---|---|---|---|-------|

| 0x000  | RESET | BOOTLOAD | SAVE  | FACTORY | -  | -  | - | - | - | - | - | - | - | - | - | PWRDN |

| Access | R/W   | R/W      | R/W-1 | R/W-1   | R  | R  | R | R | R | R | R | R | R | R | R | R/W   |

Factory default value = 0x0000

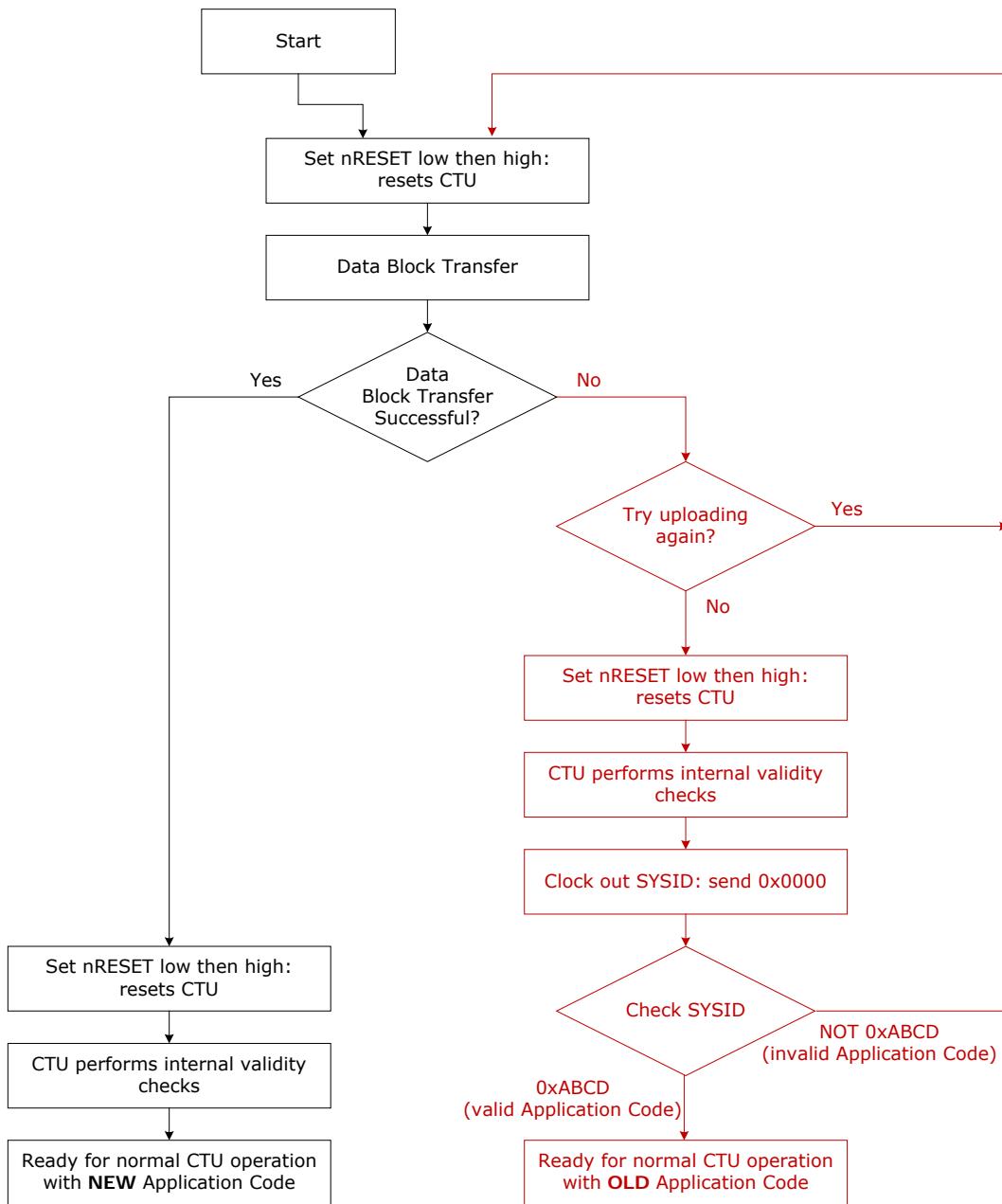

Writing a 1 to the RESET bit will result in a device reset at the end of the SPI transaction. Registers will return to their default values and measurements will be aborted. SPI transactions will be ignored until the device comes out of reset.

The PWRDN bit is not currently implemented.

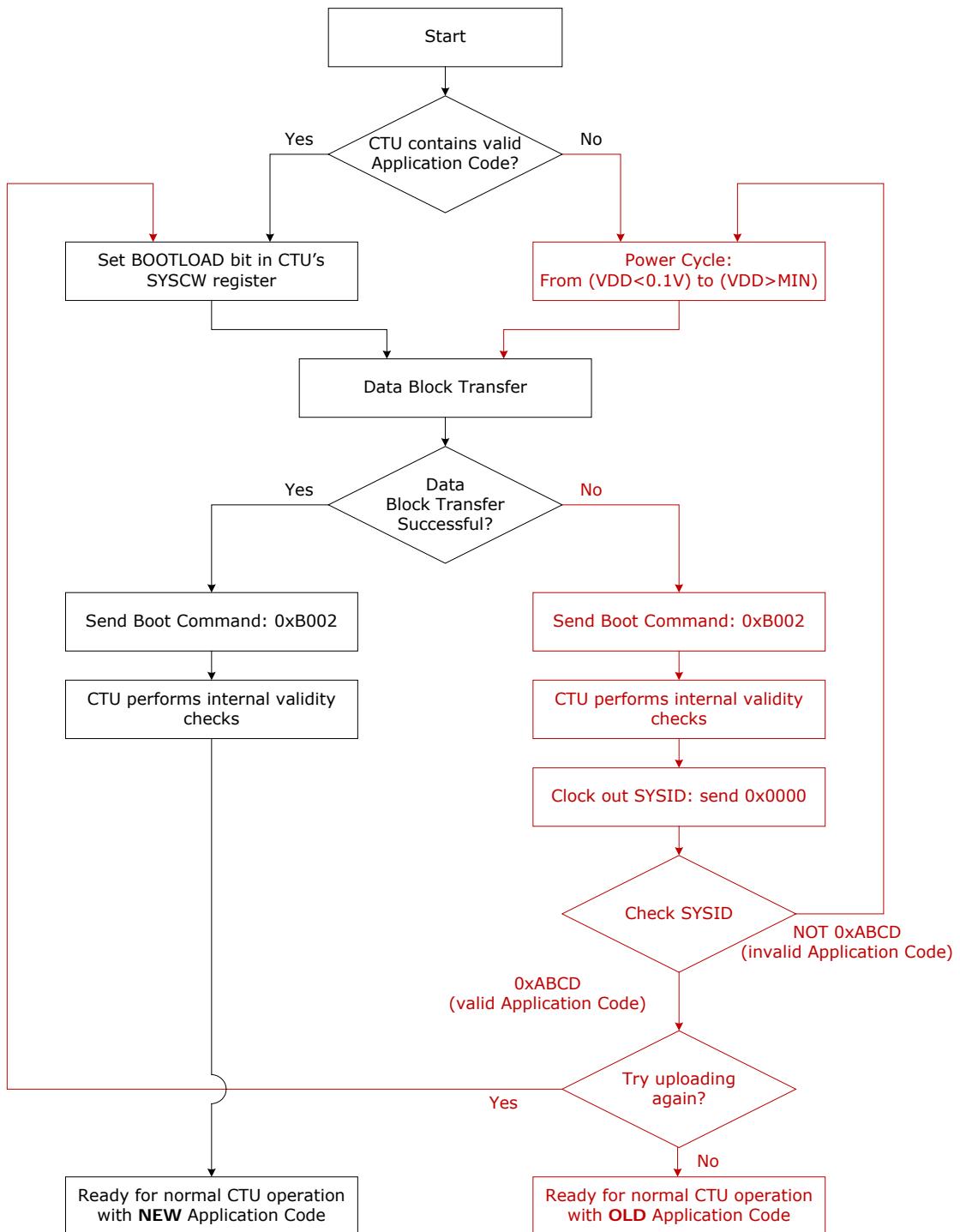

Writing a 1 to the BOOTLOAD bit resets the CTU at the end of the SPI transaction. When the CTU comes out of reset, it will remain in Bootloader Mode (section 10) until the next reset.

Writing 0x0C1C to the SAVEKEY register then 1 to the SAVE bit will result in the current register contents being made the Configurable Defaults. Writing 0x0C1C to the SAVEKEY register then 1 to the FACTORY bit, will result in restoration of the factory default register values. After SAVE or FACTORY operations the CTU will reset. Please see section 9.13 for more details.

## 8.2 SYSI: System Interval Register

| SYSI   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0           |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-------------|

| 0x001  |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | SYSI [15:0] |

| Access |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | R/W         |

Factory default value = 0x000A

In continuous mode (CONT=1), SYSI determines the interval between measurements, and is timed by the CTU. In Continuous Pipeline Mode with PIE=1 it is in multiples of 0.1µs, otherwise with PIE=0 it is in multiples of 100µs.

In Pipeline Mode with CONT=0, SYSI is used to tell the CTU what sample interval the host is using between SPI transactions, so that it can ensure fresh measurement results are available just in time for the host to read them. Writing 0 to SYSI tells the CTU to use the interval between the last two measurements as the estimate of the next sample interval (*CTU Timed Pipeline Interval*). Writing a non-zero value to SYSI tells the CTU to use that value of SYSI as the sample interval instead (*Host Timed Pipeline Interval*). Please refer to section 9.7 for details. In both cases the interval is measured in multiples of 0.1µs.

## 8.3 SYSIO: System IO Configuration

| SYSIO  | 15 | 14 | 13 | 12 | 11      | 10      | 9       | 8       | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|--------|----|----|----|----|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| 0x002  | -  | -  | -  | -  | INT 6AH | INT 6DO | INT 5AH | INT 5DO | INT 4AH | INT 4DO | INT 3AH | INT 3DO | INT 2AH | INT 2DO | INT 1AH | INT 1DO |

| Access | R  | R  | R  | R  | R/W     |

Factory default value = 0x0000

The SYSIO register controls each IO pin's behaviour. Each pin may be configured for active low or active high with the coding of Table 17. Independently, each pin may be configured for open drain or *digital* with the coding of Table 18. *Digital* means driven both high and low.

Table 17

| INTnAH | Function    |

|--------|-------------|

| 0      | Active Low  |

| 1      | Active High |

Table 18

| INTnDO | Function       |

|--------|----------------|

| 0      | Open Drain     |

| 1      | Digital Output |

#### 8.4 CTUID: CTU Identity

| CTUID  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0           |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-------------|

| 0x00B  |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | CTUID[15:0] |

| Access |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | R           |

Default value = 0x0000

This system register is not currently implemented.

#### 8.5 SAVEKEY: Save Key

| BOOTVER | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0             |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---------------|

| 0x00C   |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | SAVEKEY[15:0] |

| Access  |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | R/W           |

Default value = 0x0001

This system register is used to prevent accidental changes being made to register defaults. For the SAVE and FACTORY operations to take effect, its value should be set to 0x0C1C. Both of these operations result in an internal reset, which clears SAVEKEY back to its default, "safe", state.

#### 8.6 BOOTVER: Bootloader Version Number

| BOOTVER | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0                                |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----------------------------------|

| 0x00D   |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | Bootloader Version Number [15:0] |

| Access  |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | R                                |

Factory default value = 0x????

The BOOT register contains the fixed revision number for the CTU's Bootloader Code, and is read-only.

#### 8.7 SYSVER: System Version

| SYSVER | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0                            |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|------------------------------|

| 0x00E  |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | System Version Number [15:0] |

| Access |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | R                            |

Factory default value = 0x????

The SYSVER register contains the version number of the CTU's Application Code, and is read-only. It is updated when new code is successfully updated using the bootloader (section 10).

#### 8.8 SYSID: System Device ID

| SYSID  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0              |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----------------|

| 0x00F  |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | DEVICEID[15:0] |

| Access |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | R/W            |

Factory default value = 0xABCD

The System Device ID is a host-writeable word, and appears as the first word of every SPI transaction in normal operation (see Figure 19). It is recommended that the host verifies this value against the expected one, to assist detection of communication errors.

The Device ID may be used to identify different SPI slave devices connected to the same host. Any value may be chosen; it is of no significance to the CTU. It is recommended to avoid the codes listed in Table 27, since these are used to report status.

The Device ID may be used to detect or verify that a CTU reset has occurred. The host should write a new Device ID, and any subsequent reset will cause the Device ID to return to its default value.

## 8.9 SCW: Sensor Control Word

| SCW    | 15 | 14 | 13          | 12 | 11  | 10   | 9    | 8    | 7   | 6    | 5    | 4     | 3 | 2    | 1    | 0   |

|--------|----|----|-------------|----|-----|------|------|------|-----|------|------|-------|---|------|------|-----|

| 0xn00  |    |    | SENSOR[3:0] |    | PIE | PIF  | INCE | INCF | SIE | SIF  | NEW  | VALID | - | TRIG | CONT | GO  |

| Access |    |    | R           |    | R/W | R/W0 | R/W  | R    | R/W | R/W0 | R/W0 | R     | R | R/W  | R/W  | R/W |

Factory default value = 0xn000

The registers described above relate to system functions. The Sensor Control Word, and the other *sensor registers* described below, relate to sensors connected to the CTU. The CAM502 only supports one connected sensor, and the host must only access sensor 1 (SENSOR=1).

A sensor's SCW register controls the CTU's measurements of that sensor.

The upper 4 bits of SCW, SENSOR[3:0], is a read-only field that equals the sensor number, to help the host verify it associates results with the correct sensor.

The host can start a measurement on a sensor by setting its GO bit to 1. If the host also sets the CONT bit to 1 the CTU will measure that sensor continuously. In this case, the sample interval between measurements is configured with SYSI, see section 8.2. If a sensor's CONT bit is set to 0, setting its GO bit to 1 will result in a single shot measurement. The CTU will clear GO to 0 upon completion.

The TRIG bit is not implemented.

The VALID bit indicates that the last measurement result for the sensor was valid. The CTU sets the VALID flag when it determines the channel's target to be in range. The meaning of in range depends on the sensor and target, but typically means that it is physically aligned within specification and its resonant frequency is within the limits specified in Table 13.

The NEW flag indicates that new measurement data is available for the sensor. The CTU sets NEW to 1 when a measurement is completed. If the host uses a write read SPI operation to read results, spanning registers SCW and the desired result registers, it is recommended to clear NEW back to 0 during that transaction. That way, the host can unambiguously verify that the results it has collected from the CTU are new.

The SIF bit is the sample indicator flag, and SIE is the sample indicator enable bit. Sample indicators can be configured to activate an IO when a new, or a new valid, sensor measurement is available. The SIE bit controls whether sample indicators are enabled. Once activated, the host may clear a sample interrupt by writing a 0 to SIF.

INCE and INCF are for sensor Types 2 and 6, which support Incremental Mode. The INCE bit controls whether Incremental Mode is allowed. The INCF bit is a flag that indicates when an incremental measurement was actually performed. See section 9.8 for details.

PIE and PIF are for operation in Pipeline Mode (section 9.7). PIE enables Pipeline Mode. PIF is a flag that indicates when the sensor is being sampled in Pipeline Mode.

## 8.10 RESA...RESF: Results Registers

|                 |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |                             |

|-----------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-----------------------------|

| RESA ... RESF   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0                           |

| 0xn02 ... 0xn07 |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | RESA [15:0] ... RESF [15:0] |

| Access          |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | R                           |

Factory default values = 0x0000

A sensor's results registers contain the results of the most recent measurement. The CTU does not update the SCW and results registers during SPI transactions, to prevent data skew. So their values are effectively latched by the negative going transition of nSS.

The CTU supports different sensor types. The interpretation of result registers depends on the sensor type as detailed in Table 19.

**Table 19 Results register contents by Sensor Type**

| Register | Sensor Type                      |

|----------|----------------------------------|

|          | <b>2 and 6</b>                   |

| RESA     | CtuReportedPositionI32 high word |

| RESB     | CtuReportedPositionI32 low word  |

| RESC     | AmplitudeAU16                    |

| RESD     | AmplitudeBU16                    |

| RESE     | RelativeFrequencyI16             |

| RESF     | BAPositionMismatchI16            |

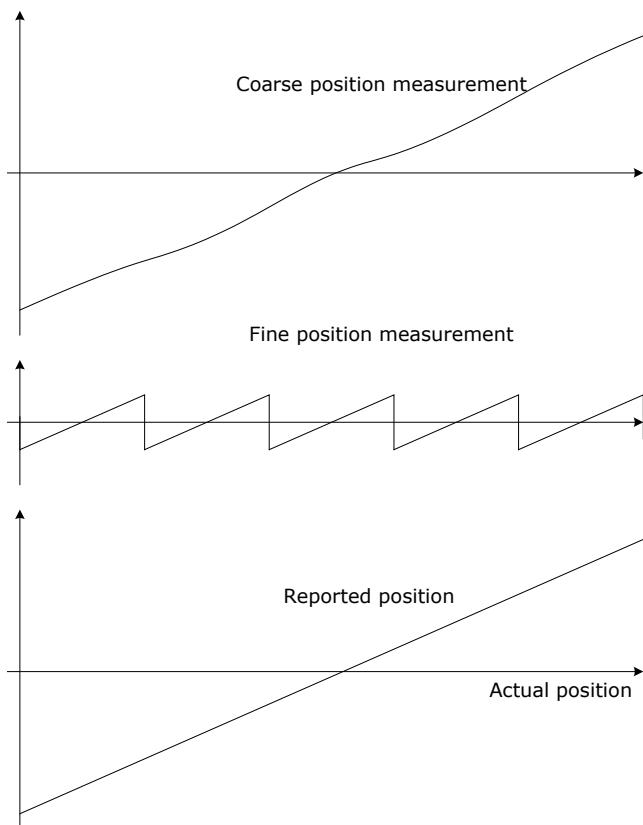

CtuReportedPosition may be converted into measurement units with Equation 3 below. Sin Length is a characteristic of the sensor, and is quoted in sensor datasheets. Type 2 and 6 sensors have fine and coarse pitches; Sin Length should be set to Fine Pitch (SinLengthA) for use in Equation 3. For full 360° rotary Type 6 sensors, SinLength equals 360°/Subtype.

$$\text{Reported Position} = \frac{\text{CtuReportedPosition}}{65536} \times \text{SinLength}$$

**Equation 3**

Note that Reported Position is a signed quantity which is nominally 0 when the Target Origin/ Reference Direction is aligned with the Sensor Origin/Reference Direction for linear/rotary sensors. This is usually at the centre point of the sensor's travel.

CtuReportedPosition will be forced to 0 following an invalid measurement when the target is out of range. The host can use the VALID bit of the SCW register to distinguish this condition from zero Reported Position.

Amplitude is a measure of inductive signal strength and influences system performance, particularly resolution (for example see section 4.4). Type 2 and 6 sensors have two Amplitude results, one derived from measurements of the fine sensor coils, *Amplitude A*, and one from the coarse, *Amplitude B*. The coarse value is usually significantly less than the fine. References to Amplitude in a sensor's datasheet are to Amplitude A unless otherwise noted.

Relative Frequency is the CTU's measurement of the frequency difference in Hz between the target and the CTU's Nominal Operating Frequency listed in Table 13.

BA Position Mismatch is specific to Type 2 and 6 sensors. It is scaled in the same way as Reported Position using Equation 3. When results are from Incremental Mode operation (INCF=1), BA Position Mismatch is the difference between the current and previous reported position. In absolute mode (INCF=0), BA Position Mismatch is the difference between position readings from the fine and coarse sensor tracks. In each of these cases BA Position Mismatch is an indication of system health. Small values are healthy, while values close to SinLength/2 indicate potential for error in position measurement caused by skipping a fine period (section 9.8).

### 8.11 CONST: Measurement Constants

| CONST  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3     | 2 | 1 | 0      |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|-------|---|---|--------|

| 0xn08  |    |    |    |    |    |    |   | - |   |   |   |   | FCSEL |   |   | ABSSEL |

| Access |    |    |    |    |    |    |   | R |   |   |   |   | R/W   |   |   | R/W    |

Factory default value = 0x000C

The CONST register includes the measurement constants FCSEL and ABSSEL.

ABSSEL may be used to specify a number of fine measurements, ABSCOUNT, to be taken in between single coarse measurements when operating in Pipeline mode, see section 9.9. The value of ABSCOUNT is given by:

$$ABSCOUNT = 2^{ABSSEL}$$

**Equation 4**

FCSEL controls whether or not the CAM502 applies digital filtering to position results, and the amount of filtering, as described in section 9.11.

### 8.12 STYPE: Sensor Type Register

| STYPE  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3                 | 2 | 1 | 0                  |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|-------------------|---|---|--------------------|

| 0xn11  | -  | -  | -  | -  | -  | -  | - | - |   |   |   |   | SUBTYPE[3:0]      |   |   | TYPE[3:0]          |

| Access | R  | R  | R  | R  | R  | R  | R | R |   |   |   |   | R/W (all sensors) |   |   | R/W (sensor1 only) |

Factory default value = 0x0002

The CTU supports different Types of sensor (Table 1). Only one Type of sensor may be connected to the CTU. Sensor 1's TYPE field is used to tell the CTU what sensor Type is connected, including when there are multiple sensors.

Some sensors have Subtypes. For example "Type 6.5" is Type 6, Subtype 5. For sensor Types that support Subtypes, the sensor's Subtype must be written to the SUBTYPE field. If the sensor Type also supports multiple sensors, SUBTYPEs may be different for each sensor. When the sensor Type does not support Subtypes, SUBTYPE must be set to 0 for each sensor used.